A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

## PERFORMANCE ANALYSIS AND IMPLEMENTATION OF HIGH SPEED FULL-ADDER USING MODIFIED GDI TECHNIQUE

SWATHI KIRAN<sup>1</sup>, M.AMARNATH REDDY<sup>2</sup>

<sup>1</sup>PG Scholar, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India <sup>2</sup> Assistant Professor, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India

**ABSTRACT:** A processor is a main part of any digital system. And an ALU is one of the main components of a microprocessor. To give a simple analogy, CPU works as a brain to any system & and ALU works as a brain to CPU. So it's a brain of computer's brain. They are consists of fast dynamic logic circuits and have carefully optimized structures. Rapid development of portable digital applications, the demand for increasing speed, compact implementation, and low power dissipation triggers numerous research efforts. The wish to improve the performance of logic circuits, once based on traditional CMOS technology, resulted in the development of many logic design techniques during the last two decades. GDI (Gate diffusion input) a technique of low power digital combinational design. This technique as compare to other currently used logic design styles, allows less power consumption and reduced propagation delay for low -power design of combinatorial digital circuits with minimum number of transistors. In this project presented with 4-bit arithmetic logical unit design with the use of Gate Diffusion Input Technique. And the ALU consist of 2\*1 and 4\*1 and full adder implementations. system robustness.

### **I.INTRODUCTION**

A adder is one of the significant building In our day by day life, we utilize a great deal of compact electronic gadgets; these gadgets fundamentally are low force rapid VLSI circuits works at the same time. One of these circuits is the Arithmetic rationale unit (ALU) which considered a fundamental part in numerous applications, for example, Microprocessor, advanced sign handling, picture preparing, and so forth. Expansion considered basic piece of the number juggling unit and practically all other number-crunching activities incorporates expansion thusly any improvement in the viper cell is reflected as a significant improvement in the ALU. In this paper a 4-Bit ALU is planned utilizing a low force snake cell acknowledged by the Full-Swing GDI procedure

A processor is a fundamental piece of any advanced framework. What's more, an ALU is one of the principle segments of a microchip. To give a straightforward relationship, CPU functions as a cerebrum to any framework and ALU fills in as a mind to CPU. So it's a mind of PC's cerebrum. They are comprises of quick powerful rationale circuits and have deliberately enhanced structures. Of complete force utilization in any processor, CPU accounts a noteworthy part of it. ALU likewise add to one of the most powerful thickness areas on the processor, as it is timed at the most noteworthy speed and is occupied for the most part constantly which brings about warm hotspots and sharp temperature inclinations inside the execution center. In this manner, this rouse us emphatically for an energyefficient ALU structures that fulfill

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

the elite prerequisites, while decreasing pinnacle and normal force dissipation.[1,2] Basically ALU is a combinational circuit that performs number juggling and sensible procedure on a couple of n bit operands for example A [0:7] and B [0:7] for 8 bits

### II. GATE DIFFUSION INPUT (GDI)

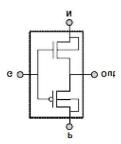

Gate Diffusion Input (GDI) method is based on the utilization of a simple cell as shown in Fig. 1 which can be used for low power digital circuits [3]. This technique is implemented in twin-well CMOS or Silicon on Insulator (SOI) technologies. In this process, the bulks of both NMOS and PMOS transistors are hardwired to their diffusions to reduce the bulk effect that is dependence of threshold voltage on source-to-bulk voltage [12]. The dependence of transistor threshold voltage on source-to-bulk voltage is as follows:

$$V_{th} = V_{th0} + \gamma \left( \sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|} \right) - \eta V_{DS}$$

Where VSB is source-body voltage, Vth0 is threshold voltage at VSB=0,  $\gamma$  is linearized body coefficient,  $\Phi$ F is the Fermi potential and  $\eta$  is Drain nduced Barrier Lowering (DIBL) coefficient. Using this procedure power consumption can be reduced along with delay time thereby delivering a reduced power delay product. Consequently area of the circuit is minimized.

Figure 1: Basic GDI Cell

It should be noted that though the circuit resembles with standard CMOS inverter, there are certain important differences compared to conventional one. The GDI cell contains 3 inputs— P which is the input to the outer diffusion node of the PMOS transistor is not connected to Vdd while N which is the input to the outer diffusion node of the NMOS transistor is not connected to GND, and G which is the common gate input of both the NMOS and PMOS transistors. The Out node which is the common diffusion of both the transistors may be utilized as input or output port depending on the circuit configuration.

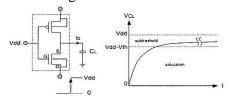

The ports P and N delivers 2 extra pins which yield the GDI design more compliant than the usual CMOS design [3]. Fig. 2 shows the transient response of a GDI cell which is quite similar to that of a standard CMOS inverter [13], [14]. This analysis is based on the Shockley model in which the drain current ID is represented as shown below

$$I_D = \begin{cases} I_{D0} \begin{pmatrix} W \\ L \end{pmatrix} \ell^{(qV_{GS}/KT)} \\ (V_{GS} \leq V_{\text{TH}} : \text{subthreshold region}) \\ K \left\{ \begin{pmatrix} V_{GS} - V_{\text{TH}} \end{pmatrix} V_{DS} - 0.5V_{DS}^2 \right\} \\ (V_{DS} < V_{GS} - V_{\text{TH}} : \text{linear region}) \\ 0.5K \left(V_{GS} - V_{\text{TH}} \right)^2 \\ (V_{DS} \geq V_{GS} - V_{\text{TH}} : \text{saturation region}) \end{cases}$$

Where K denotes device trans conductance parameter, VTH denotes threshold voltage, W denotes channel width and L denotes channel length.

Figure 2: Transient response of a GDI cell

However, it is to be mentioned that in GDI cell Vds has to be considered as a variable

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

of input voltage in Shockley model [3] in contrast with CMOS inverter analysis [15] where Vgs was considered as an input voltage.

### III.LOGIC GATES BASED ON GDI **METHOD**

Table I shows the various operations that can be performed with a basic GDI cell.

## TABLE I. DIFFERENT OPERATIONS OF BASIC GDI CELL

| N           | P   | G | Out   | Operation |

|-------------|-----|---|-------|-----------|

| <b>'</b> 0' | В   | A | ĀB    | F1        |

| В           | '1' | A | Ā+B   | F2        |

| '1'         | В   | A | A+B   | OR        |

| В           | '0' | A | AB    | AND       |

| С           | В   | A | ĀB+AC | MUX       |

| <b>'</b> 0' | '1' | A | Ā     | NOT       |

From table I, it can be noticed that using only 2 transistors various functions can be performed. For instance, OR gate can be designed using a single GDI cell whereas in case of designing of an OR gate gate can be designed using only 2 transistors and even a Multiplexer MUX) can be devised using a single GDI cell. Thus, a simple alteration to the input configuration of the GDI cell would yield myriad variety of Boolean functions. Multiple-input gates can be implemented by combining several GDI cells.

### IV PROPOSED SYSTEM

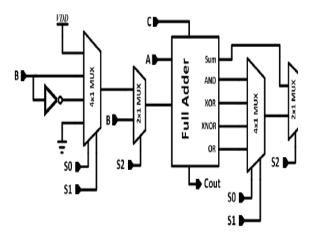

Full adder is a combinational circuit that Gate Diffusion Input Technique is another strategy for lessening power dissemination, spread postponement with less territory. We have structured ALU in various manner by utilizing GDI cells to actualize multiplexers and full viper circuit. The info and yield areas comprise of 4x1 and 2x1 multiplexers

and ALU is actualized by utilizing full adder.Ex: T. Esther Rani, M. Asha Rani, Dr. Rameshwar Rao, planned a zone advanced low force number juggling and rationale unit in which Arithmetic Logic Unit is actualized utilizing rationale doors, pass transistor rationale, just as GDI procedure

A multiplexer is a computerized switch picks the yield from a few sources of info dependent on a select sign [4], appeared in Fig. 2 a 2x1 multiplexer comprises of 6 transistors.

A number juggling rationale unit (ALU) is a crucial structure square of the Central Processing Unit (CPU) of a PC, and even the most straightforward microchips contain one. It is liable for performing number juggling and rationale tasks, for example, expansion, deduction, increase, decrement, sensible AND, legitimate OR, intelligent XOR and consistent XNOR.ALU comprises of eight 4x1 multiplexers, four 2x1 multiplexers and four full adders. The 4piece ALU is structured in 250nm, n-well CMOS innovation. At the point when rationale '1'and rationale '0' are applied as an info INCREMENT and DECREMENT tasks happens separately. An INCREMENT activity is dissected as including '1' to the numbers to be added and DECREMENT is viewed as a deduction activity [6].

| S2 | S1 | S0 | Operations   |

|----|----|----|--------------|

| 0  | 0  | 0  | DECREMENT    |

| 0  | 0  | 1  | ADDITION     |

| 0  | 1  | 0  | SUBSTRACTION |

| 0  | 1  | 1  | INCREMENT    |

| 1  | 0  | 0  | AND          |

| 1  | 0  | 1  | XOR          |

| 1  | 1  | 0  | XNOR         |

| 1  | 1  | 1  | OR           |

Two's complement method is used for SUBTRACTION in which complement of B is used. The outputs obtained from the full

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

adder are SUM, EXOR, EXNOR, AND & OR.

Fig:4.2 shows the square chart of 4-piece ALU where the primary stage to fourth stage is fell with the CARRY bit. Emblematic portrayal of 4-piece ALU has been envisioned in fig. 3. The multiplexer stage chooses the suitable sources of info dependent on the state of the select signals, and offers it to the full snake which at that processes the outcomes. point multiplexer at the yield stage chooses the suitable yield and course it to yield port. The activity being performed and the data sources and yields being chosen are controlled by set of three select signs consolidated in the structure. Fig 8. shows multiplexer rationale at input port and Fig 9. shows multiplexer rationale at yield port. The multiplexer stage chooses the proper data sources dependent on the state of the select signals, and offers it to the full viper which at that point figures the outcomes. The multiplexer at the yield stage chooses the suitable yield and course it to yield port. Table 2 shows reality table for the tasks performed by the ALU dependent on the status of the select sign.

### V IMPLEMENTATION

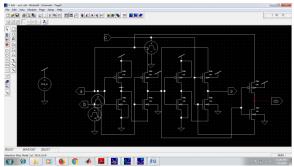

Fig 5 Circuit Design

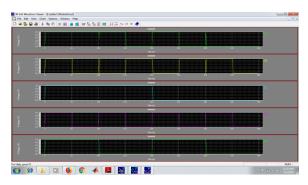

Fig 5 Simulation Result

#### VI CONCLUSION

The goal of this paper was to design a full adder with high speed performance using GDI technique. From the performance analysis table it is clear that the proposed design system is the best among the discussed designs in terms of area, delay and power dissipation. Since the results were obtained as an outcome of simulation, the readings are precise. This design will have an improved speed and also the efficiency of the system is more compared to all the conventional techniques. Further modifications can be made in the design by adding a few more transistors.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

#### **REFERENCES**

- [1] Tripti Sharma, K.G.Sharma and B.P.Singh,"High Performance Full Adder Cell: A Comparative Analysis",2010 IEEE Students' Technology Symposium 3-4 April 2010,IIT Kharagpur, 2010.

- [2] Rajkumar Sarma1 and Veerati Raju," Design and Performance Analysis of Hybrid Adders For High Speed Arithmetic Circuit", International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.3, June 2012.

- [3] A. Morgenshtein, A. Fish, and I. Wagner, "Gate-diffusion input (GDI): a power-efficient method for digital combinatorial circuits," IEEE Transactions on Very Large Scale Integration (VLSI) Systems IEEE Trans. VLSI Syst., vol. 10, no. 5, pp. 566–581, 2002.

- [4] A. Morgenshtein, I. Shwartz, and A. Fish, "Gate Diffusion Input (GDI) logic in standard CMOS Nanoscale process," 2010 IEEE 26th Convention of Electrical and Electronics Engineers in Israel, 2010.

- [5] A. Morgenshtein, V. Yuzhaninov, A. Kovshilovsky, and A. Fish, "Fullswing gate diffusion input logic—Case-study of low-power CLA adder design," Integration, the VLSI Journal, vol. 47, no. 1, pp. 62–70, Jan. 2014.

- [6] Korraravikumar, AL Reddy, M.Sadanandam, Santhoshkumar.A and M.Raju," Design of 2T XOR Gate Based Full Adder Using GDI Technique", International Conference on Innovative Mechanisms for Industry Applications (ICIMIA 2017),2017.

- [7] Jaume Segura, Charles F. Hawkins CMOS electronics: how it works, how it fails, Wiley-IEEE, 2004, page 132

- [8] Clive Maxfield Bebop to the Boolean boogie: an unconventional guide to electronics Newnes, 2008, pp. 423-426

- [9] Albert Raj/Latha VLSI Design PHI Learning Pvt. Ltd. pp. 150-153

- [10] Yano, K, et al, "A 3.8 ns CMOS 16\*16b multiplier using complementary pass transistor logic", IEEE J. Solid State Circuits, Vol 25, p388-395, April 1990

- [11] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "A Novel Multiplexer-Based Low-Power Full Adder" IEEE Transaction on circuits and systems-II: Express Brief, Vol. 51, No. 7,p-345, July- 2004

- [12] Makoto Suzuki, et al, "A 1.5 ns 32 b CMOS ALU in double pass transistor logic", ISSCC Dig. Tech. Papers, pp 90-91, February 1993.

- [13] N. Ohkubo, et al, "A 4.4 ns CMOS 54X54 b multiplier using pass transistor multiplexer", Proceedings of the IEEE 1994 Custom Integrated Circuit Conference, May 1-4 1994, p599-602, San Diego, California.

- [14] Mohamed W. Allam, "New Methodologies for Low-Power High-Performance Digital VLSI Design", PhD. Thesis, University of Waterloo, Ontario, Canada, 2000

- [15] A.Bazzazi and B. Eskafi, "Design and Implementation of Full Adder Cell with the GDI Technique Based on 0.18µm CMOS Technology", International MultiConference of Engineers and Computer Scientists (IMES) Vol II, March 17 19, 2010, Hong Kong