A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

# PERFORMANCE EVALUATION OF 10T SRAM CELL BY USING THE ADIABATIC PRE-CHARGE UNIT TECHNIQUE

<sup>1</sup>K SRAVANI, <sup>2</sup>K.VENKANNA

<sup>1</sup>PG SCHOLAR, SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

<sup>2</sup>ASSOCIATE PROFESSOR THE DEPARTMENT OF ECE IN SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

#### **ABSTRACT:**

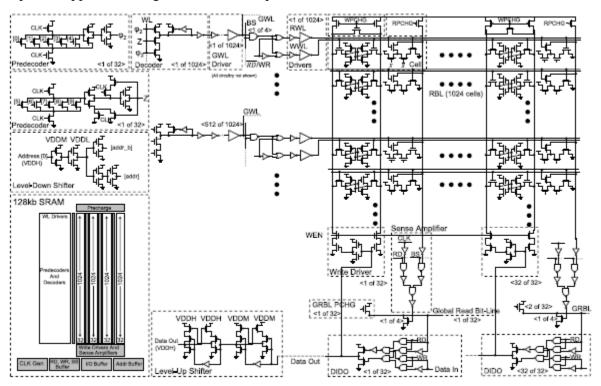

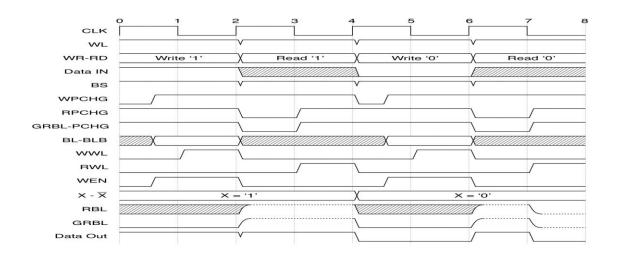

The regular six-semiconductor static irregular access memory (SRAM) cell permits high thickness and quick differential detecting yet experiences half-select and read-upset issues. In spite of the fact that the traditional eight-semiconductor SRAM cell addresses the read-upset issue, it actually experiences low cluster proficiency because of disintegration of read bit-line (RBL) swing and Ion/Ioff proportion with increment in the quantity of cells per section. Past ways to deal with tackle these issues have been tormented by low execution, information subordinate spillage, enormous territory, and high energy per access. There-front, in this paper, we present three cycles of SRAM bit cells with nMOS-just based read ports meant to extraordinarily decrease information subordinate read port spillage to empower 1k cells/RBL, improve read execution, and lessen territory and control over ordinary and 10T cell-based works. We contrast the proposed work and different works by recording measurements from the recreation of a 128-kb SRAM built with separated wordline-unraveling design and a 32-bit word size. Aside from huge enhancements saw over customary cells, up to 100-mV improvement in read-access execution, up to 19.8% saving in energy per access, and up to 19.5% saving in the zone are additionally seen over other 10T cells, consequently growing the plan and application array for memory planners in low-power sensors and battery-empowered gadgets.

#### INTRODUCTION:

STATIC Random Access Memory (SRAM) involves a huge bit of a framework on-a-chip (SoC) and has a striking commitment to the absolute force utilization and territory of the SoC. Since territory is a significant factor when planning circuits, memory configuration engineers plan to put the same number of cells as conceivable per section to permit sharing of

fringe hardware. The regular 6T and 8T cells are extraordinarily restricted by their powerlessness to work in longer segments. This is on the grounds that they experience the ill effects of information subordinate spillage and corrupted ION/IOFF proportion and read bit-line swing as more cells are put on a solitary segment. Accordingly, there is a need to plan new circuits to address this issue. Past methodologies [1]–[3]

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

have attempted to tackle this issue by improving the ION/IOFF proportion to empower up to 1k cells per section. In spite of the fact that these methodologies have been effective at this errand, these still experience the ill effects of huge zone or shifting information subordinate execution. Some likewise fall flat to represent the base energy point in SRAMs and hence, burn-through a great deal of energy per access at super low voltages. This work depicts three cycles of SRAM bit cells with nMOS-just based read ports intended to enormously information subordinate read port spillage to empower 1k cells per RBL, improve read execution, and diminish territory and control over ordinary 6T and 8T cells and other novel read-port based cells. With an exceptional geography in every one of the three cells' perused port, we get improved perused admittance execution, low energy per access, and low region individually, consequently developing the plan and application range for memory planners in low power sensors and battery empowered gadgets. SRAM's effect has gotten particularly significant due to the rise of battery fueled convenient gadgets and low power sensor applications. Most SRAM plan exertion has been prompted encourage voltage scaling and improving yield. The customarily executed six semiconductor (6T) cell in SRAMs permits high thickness, bit-interleaving and quick differential detecting be that as it may,

experiences half-select solidness, read-upset security, what's more, clashing peruse and compose measuring. Past endeavors to settle these issues have incorporated the usage of help novel cell plan, compositional methods, upgrades, or then again mechanical turns of events. Half-select and read-upset issues in SRAMs can be alleviated by advancement of word-line voltage level. This incorporates wordline under-drive helps utilizing measure corner following [4] or on the other hand utilizing copy access semiconductors [5]. Deferred word-line help [6] to coordinate the inside voltage of halfchose cells to that of the digit line during a read activity assists with improving their soundness yet requires adjusting to set up the delicate tradeoff between read soundness and compose capacity. Cell supply help can likewise be utilized to improve half-select security by expanding the drive strength of pull down nMOS.

#### **RELATED WORD:**

Aside from help strategies, enhancements for the design front have likewise been made to address half-choose and readdisturb steadiness issues. These incorporate cross-point determination of words utilizing both line and section word-lines to improve half select solidness [13], [14]. More limited piece lines can likewise be used to improve read soundness. These work by decreasing bitline capacitance, in this manner

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

improving powerful read edge. In any case, this comes to the detriment of huge zone overhead due to more prominent number of cell banks. In another work [15], an exhibit design with a zone overhead of 12% was executed to address the half-select upset issue by decoupling the enormous piece line capacitance from half-chose cells. Readand- compose back plan [3] has additionally been utilized to lighten the compose upset into equal parts select cells. It permits information maintenance by composing back the away information after each read. Nonetheless, such strategies increment the dynamic force utilization since each section is exposed to full voltage swings. Moreover, the sense enhancer can't be shared among a few segments furthermore, must be coordinated in every section, in this manner bringing about a enormous region overhead. With the 6T SRAM cell being distressed by different solidness issues, the 8T SRAM cell has been proposed (appeared in Fig. 1). It has a decoupled perused way including two nMOS semiconductors. Despite the fact that it takes out the read-upset issue, it is Fig. 1. Schematic of (a) 6T (b) 8T SRAM cell. still beset by a pseudo-read during a compose activity in half-chose cells on a similar column. Thusly, the issue of loss of touch interleaving capacity emerges. interleaving is basic to low voltage SRAM activity since it is joined with Error-Correction Code (ECC) to battle delicate mistakes and accomplish required yield targets. Delicate mistakes, including Single Touch Upsets (SBUs) and Multiple Cell Upsets (MCUs) are brought about by assault of alpha-particles, warm neutrons or on the other hand high energy grandiose beams [16]. The pace of delicate blunders increments by 18% for each 10% decline in stock voltage [17]. This is particularly dangerous for low voltage SRAMs, since in subedge activity area, the basic charge in hubs is fundamentally diminished, prompting continuous MCUs [18]. In [19] and [20], MCUs have been moderated by executing and joining bit-interleaving structure with ECC. Furthermore, bit-interleaving fit cell structures such as the segment decoupled 8T cell in [21], upset free 9T cell in [13], two-port upset free 9T cell in [22], multi-port 9T cell in [23] and the differential 10T cell in [24] have been proposed to empower bit-interleaving and eliminate halfselect upset issues by utilizing both line and section word-lines. For cell structures without interleaving ability, for example, the single finished 8T cell, extra equality or ECC pieces can be interleaved per word for delicate blunder remedy flood botch in the accompanying stage will occur if the current stage is a screw up and besides 0x . . . FF. This can be recognized by AND ing the incrementer carryout with the accompanying stage invalid register. Beginning bumbles can be recognized by taking care of the as of late decoded stages in snares and

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

differentiating and a counter that screens the current stage number. If the current stage is identical to the as of late decoded regard, the accompanying stage will have a hidden misstep. The counter simply needs to check to M and subsequently needs y = log2(M) bits. Consequently, simply a y-digit relationship should be made between the past decoded state and the counter, so Z = (y/n) stages should be taken care of. The zeros register is used to ensure that each and every other piece in the as of late decoded regard are zero so the connection is considerable.

#### **EXPERIMENTAL RESULTS:**

The fundamental flip-flop utilized in the plan is appeared in Fig. 5. This is a unique

flip-flop with additional transistors M2 and M8 that reset the flip-flop by depleting the parasitic capacitor. The flip-flop should be continually invigorated to keep spillage from the parasitic capacitor releasing the state. M10–M13 were included as transmission doors from the yield to the contribution to permit the flip-failure to be timed without evolving state. The n-bit move register is shaped by anchoring n flip-flops. The yield of the flip-flop is just determined, while the clock is high, so a cushion is required for each flip-lemon to guarantee that the D input is constantly determined when the empower signal changes.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

An entrance disappointment happens when the read bit-line neglects to grow restrictively inside the length of the beat width of the clock. For differentially detecting cells, the entrance time is determined till the advancement of differential voltage between bit-lines. For single finished cells, the entrance time is determined as the complete time passed from worldwide word-line empower to worldwide read bit-line assessment. The going all out detecting of single finished cells is much more slow than differential detecting, in this manner expanding the absolute access time and disappointment likelihood. The likelihood of access disappointment has been determined for a  $3\sigma/\mu = 30\%$  variety in VTH utilizing the strategy gave in [34]. The entrance Vmin is resolved at the 6σ disappointment likelihood (i.e., when PFAIL = 10-9) and is appeared in Fig. 11. Four instances of working recurrence comparing to the deferral of 549-FO4, 599-FO4, 649-FO4 and 699-FO4 inverters have been thought of. As found in Fig. 11, all proposed read ports have lower access disappointment likelihood than past work. The proposed 10T-P1 cell, which is focused on elite, has an entrance Vmin of 483mV in the best case, which is doing

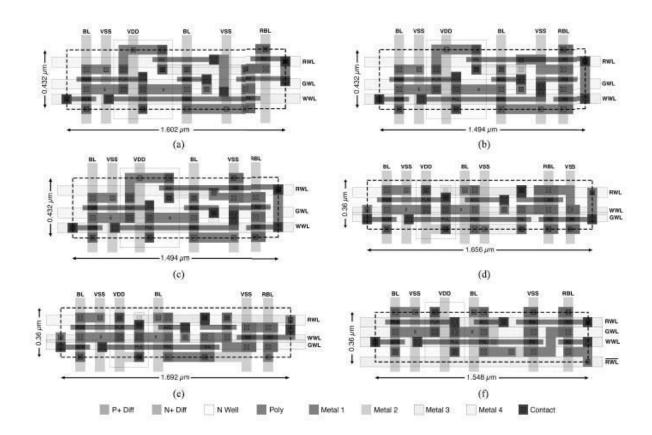

about 100mV lower than the past 10T cell-based works. At the end of the day, the 10T-P1 cell can be run at higher recurrence than different cells at some random voltage. the 32nm innovation hub ( $\lambda = 0.018 \mu m$ ). the outright and standardized territory examination is appeared in Table II. As noticed in Fig. 12, the cells from past works have extra executions of pMOS other than the inverter pair. This expands the n-well size, which prompts longer vertical estimating also, eventually longer piece lines. In this way, the dynamic read execution and force utilization are likewise disintegrated. Then again, all proposed cells have more modest vertical measuring, which prompts more modest piece line capacitance, subsequently diminishing force utilization and expanding execution. As found in Fig. 12, the 10T-C cell has the biggest region, while the proposed 10T-P3 cell has the least zone. When looking at

#### **CONCLUSION:**

In this work, we introduced three specialty explicit read ports with upgraded information free read port spillage for SRAM cells focused on superior, low force and low zone separately. Every one of the three proposed read ports didn't execute any pMOS, consequently prompting more modest n-well size, which thus prompted more modest vertical measuring and more limited piece lines in the meager structure designs. This diminished the zone per cell and

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

energy per access. Every one of the SRAM cells with the proposed peruse ports improved the compelling read bit-line voltage swing also, empowered 1k cells per read bit-line, permitting incredible potential for zone saving regarding sharing fringe hardware. With an exceptional geography in every one of the three cells' perused port, we acquire a best-case access Vmin of 483mV for the 10T-P1 cell, an Emin of 7.19pJ/acc for the 10T-P2 cell, and a low territory of 0.55728µm2 for the 10T-P3 cell. In examination to ordinary cells, this makes an interpretation of to up to 180mV improvement in read admittance execution and up to multiple times decrease in energy per access at their particular Vmin. When contrasted with past 10T cell-based works, about 100mV improvement in read admittance execution, up to 19.8% saving in energy per access, and up to 19.5% saving in zone can be noticed, accordingly expanding the plan and application array for memory creators in low force sensors and battery empowered gadgets.

#### **REFERENCES:**

[1] B. H. Calhoun and A. P. Chandrakasan, "A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation," *IEEE J. Solid-State Circuits*, vol. 42, no. 3, pp. 680–688, Mar. 2007.

- [2] G. Pasandi and S. M. Fakhraie, "A 256-kb 9T near-threshold SRAM with 1 k cells per bitline and enhanced write and read operations," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 11, pp. 2438–2446, Nov. 2015.

- [3] T.-H. Kim, J. Liu, J. Keane, and C. H. Kim, "A 0.2 V, 480 kb subthreshold SRAM with 1 k cells per bitline for ultra-low-voltagecomputing," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 518–529,Feb. 2008.

- [4] V. P.-H. Hu, M.-L. Fan, P. Su, and C.-T. Chuang, "Analysis of GeOI FinFET 6T SRAM cells with variation-tolerant WLUD read-assist and TVC write-assist," *IEEE Trans. Electron Devices*, vol. 62, no. 6, pp. 1710–1715, Jun. 2015.

- [5] S. Ohbayashi *et al.*, "A 65-nm SoC embedded 6T-SRAM designedfor manufacturability with read and write operation stabilizing circuits," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 820–829, Apr. 2007.

[6] M. E. Sinangil, H. Mair, and A. P. Chandrakasan, "A 28 nm high-density 6T SRAM with optimized peripheral-assist circuits for operation down to 0.6 V," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers*, Feb. 2011, pp. 260–262.

- [7] M. Yabuuchi, K. Nii, Y. Tsukamoto, S. Ohbayashi, Y. Nakase, and H. Shinohara, "A 45 nm 0.6 V cross-point 8T SRAM with negative

2008.

### International Journal For Advanced Research In Science & Technology

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

biased read/write assist," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2009, pp. 158–159.

[8] B. Zimmer *et al.*, "SRAM assist techniques for operation in a wide voltage range in 28-nm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 12, pp. 853–857, Dec. 2012.

[9] H. Pilo *et al.*, "A 64 Mb SRAM in 32 nm high-*k* metal-gate SOI technology with 0.7 V operation enabled by stability, write-ability and read-ability enhancements," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 97–106, Jan. 2012.

[10] A. J. Bhavnagarwala *et al.*, "A sub-600-mV, fluctuation tolerant 65-nm CMOS SRAM array with dynamic cell biasing," *IEEE J. Solid-*

[11] M. H. Abu-Rahma, M. Anis, and S. S. Yoon, "A robust single supply voltage SRAM read assist technique using selective precharge," in *Proc. 34th Eur. Solid-State Circuits Conf.*, 2008, pp. 234–237.

State Circuits, vol. 43, no. 4, pp. 946–955, Apr.

[12] D. Anh-Tuan, J. Y. S. Low, J. Y. L. Low, Z.-H. Kong, X. Tan, and K.-S. Yeo, "An 8T differential SRAM with improved noise margin for bit-interleaving in 65 nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 6, pp. 1252–1263, Jun. 2011.

[13] K. Shin, W. Choi, and J. Park, "Half-select free and bit-line sharing 9T SRAM for reliable supply voltage scaling," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 8, pp. 2036–2048, Aug. 2017.

[14] M.-H. Tu *et al.*, "A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1469–1482, Jun. 2012.

#### **Student Details:**

K Sravani, MTech Sree Vahini Institute of Science & Technology.

#### **Guide Details:**

K Venkanna,, Associate Professor in Sree Vahini Institute of Science & Technology.

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in