A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

ANALYSIS OF LOW POWER 10T SRAM CELL

USING COLUMN-SELECTION-ENABLED TECHNIQUES

KOLUSU SUBRAHMANYESWARA RAO<sup>1</sup>, T.RAJESWARI<sup>2</sup>

1PG SCHOLAR.DEPT OF ECE, SIR C.V. RAMAN INSTITUTE OF TECHNOLOGY & SCIENCE,

AP, INDIA

<sup>2</sup> ASST. PROFESSOR, DEPT OF ECE, SIR C.V. RAMAN INSTITUTE OF TECHNOLOGY & SCIENCE, AP, INDIA

#### **ABSTRACT**:

Static Random Access Memory (SRAM) involves a huge bit of a framework on-a-chip (SoC) and has an eminent commitment to the all out force utilization and zone of the SoC. Since zone is a significant factor when planning circuits, memory configuration engineers mean to put whatever number cells as would be prudent per section to permit sharing of fringe hardware. The traditional six-semiconductor static irregular access memory (SRAM) cell permits high thickness and quick differential detecting however experiences half-select and read-upset issues. In spite of the fact that the customary eight-semiconductor SRAM cell understands the read-upset issue, it actually experiences low cluster effectiveness because of disintegration of read bit-line (RBL) swing and Ion/Ioff proportion with increment in the quantity of cells per section. A nondestructive section choice empowered 10T SRAM for forceful force decrease is introduced in this brief. It liberates a half-chose conduct by misusing the bitline-shared information mindful compose conspire. The differential-VDD (Diff-VDD) method is received to improve the compose capacity of the plan. Furthermore, its decoupled read bitlines are allowed to be charged and released relying upon the put away information bits. In mix with the proposed dropped-VDD biasing, it accomplishes the critical force decrease.

### 1 INTRODUCTION

The ultralow-voltage operation of digital circuits offers a niche for applications with high constraints on energy efficiency or low power consumption, such as implantable instruments, biomedical devices, and wireless sensors. Compared with other circuits, SRAM has always drawn much more attention in low-voltage regions since it places a restriction on VDD scaling and dominates the major power and performance of the chips.

Static Random Access Memory (SRAM) occupies a significant portion of a system-on-a-chip (SoC) and has a notable contribution to the total power consumption and area of the SoC. Since area is an important factor when designing circuits, memory design engineers aim to place as many cells as possible per column to allow sharing of peripheral circuitry. The conventional 6T and 8T cells are greatly

limited by their inability to work in longer columns. This is because they

suffer from data dependent leakage and degraded ION/IOFF ratio and read bit-line swing as more cells are placed on a single column. Therefore, there is a need to design new circuits to address this issue.

Traditional 6T SRAM widely used in commercial ICs has been a workhorse for many years. While providing beneficial concerning area efficiency, it is associated with the challenge of read stability and write ability in low-voltage domains toward process, voltage, and temperature variations, thus resulting in the degraded circuit behavior or ever failure. The major reason for the VDD min limitation in 6T SRAM is the contradiction between read and write requirements as well as the direct-read-access mechanism [1].

To realize the low-voltage operation, a superior alternative is the single-ended 8T (SE-8T)

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

SRAM cell [2]. It separates the read path from the cell core by adding an isolated 2T read port, enabling read and write VDD mins to be capable of optimizing independently. Of course, several other typical SRAM cells [3]-[8] are also proposed for low-voltage applications. However, most of these new SRAM cells, including the SE-8T cell, suffer from the half-select disturbance. In other words, they are not able to support the bitinterleaving (as well as called column selection) architecture which is extensively utilized in SRAMs to afford soft error immunity in combining with the error correction code [9]. Therefore, some bit-inter leaving enabled SRAM cells are preferred to be the SRAM design. in representative one is the differential 10T (Diff-10T) bitcell [10]. It uses row-wise and columnassists to form the cross-point configuration to eradicate the half-select problem together with the read destruction. Nevertheless, this bit cell circuit has more transistors, introducing remarkable overhead. To make the matter worse, its write performance and write noise margin (WNM) are seriously exacerbated by the existence of the series-connected write access mechanism. Although the area cost is completely acceptable in advanced ultra deep-sub micrometer regions, the poor write ability imparts a limitation on VDD min

#### 2.SRAM CELL

The memory cell is the basic structure square of PC memory. The memory cell is an electronic circuit that stores the slightest bit of paired data and it must be set to store a rationale 1 (high voltage level) and reset to store a rationale 0 (low voltage level). Its worth is kept up/put away until it is changed by the set/reset measure. The incentive in the memory cell can be gotten to by understanding it.

Over the historical backdrop of processing, diverse memory cell models have been utilized,

including center memory and air pocket memory. Today, the most well-known memory cell design is MOS memory, which comprises of metal—oxide—semiconductor (MOS) memory cells. Present day arbitrary access memory (RAM) utilizes MOS field-impact semiconductors (MOSFETs) as flip-flops, alongside MOS capacitors for specific kinds of RAM.

### 3.EXISTING METHOD

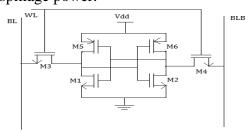

6T SRAM cell configuration utilizes bi-stable hooking hardware to store a piece (M1, M2, M5 and M6) and two access semiconductors (M3 and M4). Word Line (WL) is associated with the entrance semiconductors at their individual door terminals. WL is utilized to choose the cell. Source/Drain terminals are associated with the Bit Lines (BL and BLB), which are utilized to play out the peruse and compose procedure on the cell [5]. The issue related with mass MOSFET based 6T SRAM cell during read activity is, the point at which the WL is turned ON, it raises the yield voltage at hub that stores "0", which could turn the contrary inverter pull ON semiconductor, when this happens the voltage at hub which stores "1" will be decreased. This voltage may drop nearly nothing, however it ought not dip under the limit voltage. In the event that it dips under the limit voltage of MOSFET, it prompts read ruinous activity. Because of this solidness of the 6T SRAM cell will be debased. The activity of composing is refined by compelling the slightest bit line low while other piece line stays at about Vdd, which could prompts improvement in unique force utilization. With innovation scaling, in the new coming assembling measure the working voltage and limit voltage abatement and it annihilates the soundness of the SRAM cell. Because of the immediate ways between bit lines to the capacity hubs, the information put away in traditional SRAM cell effortlessly weakened by the outer commotion. In view of

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

the above reasons mass MOSFET based 6T SRAM cell isn't appropriate for constant video applications [10]. Henceforth we require another plan for high dependability, low unique and spillage power.

Fig 1: conventional 6T SRAM cell.

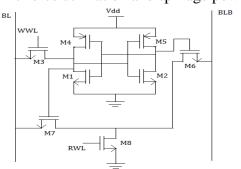

A tale 8T SRAM cell structure to lessen the spillage current and dynamic force utilization has been accounted for in this work. The schematic of proposed 8T SRAM cell at 65nm innovation is as appeared in fig. 3. The proposed SRAM cell made out of compose access semiconductor (M3), constrained by Write Word Line (WWL) and read admittance semiconductor (M8) is constrained by the Read Word Line (RWL). During the compose activity WWL is changes to high esteem and RWL and BLB both are kept up at Vgnd Hence, the read admittance semiconductor (M8) cut OFF. To compose "1" into the cell Bit Line (BL) is pre charged to a high worth, at that point "1" is constrained through the semiconductor compose access (M3).Correspondingly, to compose ,,0" into the cell, BL is released. Consequently, to perform compose activity the proposed cell using single BL, which could prompts decrease in the dynamic force utilization and spillage power.

### Fig 2 8T SRAM cell design

During read activity, RWL is change to high esteem and WWL is kept up at Vgnd Hence the compose access semiconductor is cut OFF. Preceding read activity BL and BLB are pre charged to. Accept that "1" is put away left and "0" is put away right side, at that point BL released through M7 and M8. Since, "M6" is cut OFF there is no way to release the BLB. Thus BLB is held at high worth. On the other hand, if "1" is put away right side, BLB is released through "M6" and "M8". Since, "M7" is cut OFF there is no way exists to release the BL. Thus, it can keep up at high worth. With this, stockpiling hubs totally separated from the Bit Lines (BL) during read activity, subsequently security increments altogether.

### **4.PROPOSED METHOD**

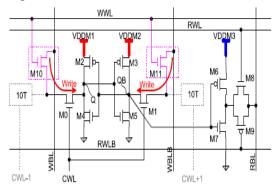

The first SE-10T SRAM cell of the proposed bit cell is appeared in Fig. 5.1. A 4T read port made out of an inverter and a transmission door (TG) is added to the 6T cell, segregating the read way from inward capacity hubs. The inverter (M6 and M7) is driven by hub QB and drives the read bitline (RBL) through TG (M8 and M9) which is constrained by two reciprocal read wordlines (WLs). This SE-10T cell can completely charge or release RBL without anyone else during a read activity. Accordingly, it is absolutely superfluous to set up a precharge circuit for RBL. The dynamic force is devoured on RBL exactly when the read datum is changed. In other words, the dynamic force scattering on RBL is zero if back to back "0"s or sequential "1"s are perused out. This component makes it reasonable for video preparing since picture information have the exceptional relationship, and comparative information are perused out in continuous cycles [11]. Sadly, because of its 6T-like compose activity, while starting a write in a segment determination exhibit, unselected cells in succession (or called half-chose cells) on the chose WL perform sham read which

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

shows that the phones simply go through a read conduct as opposed to readout during a compose activity, along these lines encountering the capacity hub upset like read upset in the 6T cell. As it were, it isn't qualified for the touch interleaving design. Also, the full rail-to-rail swing happened on RBL innately disseminates more force contrasted and the differential readout. Then, bitlines cause more spillage current in view of TG.

Fig.3. Proposed SE-10T SRAM cell.

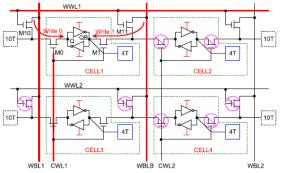

Our proposed 10T (from there on called P-10T) circuit geography is not quite the same as the prior plan. Fig. 5.1 shows the P-10T dependent on the SE-10T cell. It displays enhancements in the accompanying angles contrasted and the past circuit. Most importantly, the bitlineshared information mindful plan is embraced to empower the section choice engineering. In Fig. 5.1, the 6T part of the SE-10T cell is persuaded by the y-bearing (segment course) WL [column WL (CWL)]. Moreover, two extra access semiconductors (M10 and M11) are added to associate the 6T cell, which are initiated by the x-heading (line course) compose WL (WWL) and simultaneously are controlled by a reciprocal compose bitline pair (WBL and WBLB). Each additional entrance semiconductor and compose bitline are shared by two neighboring 10T cells in succession. During a compose activity, the information are composed into the capacity center from shared compose bitlines by means of admittance semiconductors and inward access

semiconductors, exactly when line WL and segment WL are totally turned ON. The proposed bit-interleaving-empowered plan is not the same as the past plan in [12] where the SRAM exhibit is additionally ready to be segment interleaved by vertical and flat WLs. Regardless, its compose access gadgets are shared by a few bitcells in a segment, though the compose access ones are shared by two bitcells in succession in our plan.

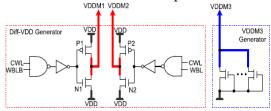

Fig.4 Diff-VDD Generator

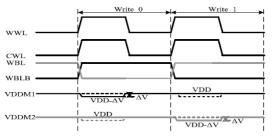

Second, a Diff-VDD procedure is used to enhance the cell's compose capacity. We can see from Fig. 5.2 that the force supplies of the 6T cell are coupled to two distinctive virtual electrical cables (VDDM1 and VDDM2) created by the Diff-VDD generator. In that, VDDM1 is created by ANDing CWL and WBLB to drive a force ON inverter, in which the source terminals of pMOS and nMOS are totally associated with VDD. So also, VDDM2 is acquired by ANDing CWL and WBL to drive the other force ON inverter. These two VDDM lines are dropped differentially as indicated by the estimations of the necessary composed information. VDDM1 line dropped at a compose access for a "0" datum on WBL (WBLB = 1), while VDDM2 line is conversely dropped for a "1" compose access. At last, we utilize a dropped-VDD biasing for the read port, bringing about absolutely recognizable force decrease. As appeared in Fig. 5.2, the force gracefully of the 4T read port is one-sided over a virtual electrical cable VDDM3 which is created through a few diodeassociated nMOSs. By and large, a voltage drop (equivalent to Vthn around) is set up over these diode-associated nMOSs, making RBL

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

swing decay to VDD -|Vthn|. Thus, much force sparing is achieved for a read activity. Ordinarily, the estimations of the VDDM1, VDDM2, and VDDM3 all equivalent to roughly 0.75 V at VDD = 1.0 V in this plan in a 65-nm CMOS, while the estimation of 0.39 V is gotten at VDD = 0.5 V. As a matter of fact, the force drivers of these three virtual electrical cables likewise present territory overhead. It is assessed that under 5% region commitment to the all out exhibit region is accomplished for the drivers.

Fig. 5. Matrix of  $2 \times 2$  with the proposed bitinterleaving architecture

The segment determination empowered ability of the proposed plan, a network of 2 lines by 2 segments  $(2\times2)$  as an illustration to portray the rudimentary compose operational rule of the exhibit is appeared in Fig. 5.3. Assume the cell1 is picked for compose. The comparing line WL WWL1 and CWL CWL1 are turned ON, and the coordinated WBLs (WBL1 and WBLB) are charged or released relying upon the information. On the off chance that a "0" is relied upon to be composed into the cell1, WBL1 is pulled down to low, and WBLB dwells at high. Accordingly, capacity hub Q is released to "0" by access semiconductors M0 and M10. At that point, the other stockpiling hub QB is pulled up to "1" through the interior cross-coupled criticism circle of the cell center. In a similar way, stockpiling hub QB is headed to "0" by access semiconductors M1 and M11 (WBL = 1 and WBLB = 0), and hub Q is charged to "1" by the positive criticism circle, demonstrating an effective express "1." For the half-chose cell2, the state hubs are not bothered during the compose period, on account of the CWL CWL2 turned OFF. Additionally, the other half-chose cell3 holds its states since the column WL WWL2 stays at low, despite CWL1 ON. By and large, the proposed 10T SRAM cluster can guarantee the half-chose cells half-select-upset free paying little mind to in succession or in a section.

The proposed plan uses the line and section coordination methods of WLs to kill the half-determination issue, which prompts the corruption in the compose capacity because of the arrangement associated compose access nMOSs simply like in the Diff-10T cell. This could be profoundly hazardous, especially in the moderate nMOS quick pMOS (SNFP) corner, where the determined quality of nMOS is not as much as that of pMOS.

To tackle this issue, the Diff-VDD conspire (appeared in Fig. 5.2) is introduced. Fig. 5.4 shows the compose waveforms of the cell to portray the compose associate circuit how to function. For the most part, VDDM1 and VDDM2 are generally proportional to VDD on the grounds that the pMOSs P1 and P2 in the Diff-VDD generator (Fig. 4.2) with crumbled VDD and P-10T. are both turned on (CWL = 0). During a state "0" activity, WLs WWL and CWL are turned on, while bitline WBL is set to low and WBLB goes to high. Along these lines, the nMOS N1 is ON (CWL and WBLB = 1), bringing about a \_V voltage drop on VDDM1. As of now, VDDM2 lives at VDD since CWL ANDing WBL approaches 0. The dropped VDDM1 can constrict the pullup quality of pMOS M2 successfully, making the fell admittance nMOSs M0 and M10 completely pull the capacity hub Q down to "0."

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

Fig. 6. WNM and write speed comparisons between Diff-10T and Diff-10T

Under a similar condition, WBL goes to high, and WBLB is headed to low start a state "1" conduct. So also, a decrease of \_V on VDDM2 power rail (CWL and WBL = 1) subverts the draw up quality of pMOS M3 to guarantee that the hub QB can be released to "0" unquestionably by M1 and M11. The proposed Diff-VDD applies a conspicuous worthwhile effect on the compose capacity, encouraging the compose activities.

In spite of the fact that the Diff-VDD compose technique can improve the compose capacity of the cell, the brought down VDDM rails represent a negative impact on the hold commotion edge (HNM) of the half-chose cells in a section.

SE-8T SRAM typically utilizes a powerful various leveled bitline conspire for readout. It requires precharging circuits to charge the bitlines after read, presenting an immense measure of intensity. A 4T read port simply like in SE-10T is used in our proposed plan with non-precharging circuits. All the more critically, we receive the dropped-VDD procedure to stifle the bitline swing, forcefully diminishing the force utilization. Obviously, this would present 16% and 10% defer debasements in read "0" and read "1." The force rails of the 4T read port of all cells in a section are outfitted by VDDM3. A nearby bitline (LBL) joined eight bitcells is associated with a worldwide bitline (GBL) through a firststage tristate support (TSB), in which an inverter with low limit (LVT) nMOS and high VT (HVT) pMOS is utilized to guarantee that the diminished swings on LBL can be enhanced. Next, GBLs are coupled to the second-stage TSBs constrained by the section select signs.

### **5.CONCLUSION**

A section choice empowered SE-10T SRAM is introduced in this brief. The bitline-shared information mindful plan and Diff-VDD are utilized to empower the spot interleaving and improve the compose capacity of the cells. In addition, a dropped-VDD strategy for power decrease is additionally proposed. The test results show that a 10T SRAM in a 180-nm CMOS accomplishes 3.3× improvement in the compose edge, along with decrease in unique force dispersal and sparing in spillage power utilization contrasted and past individually.

### REFERENCES

- [1] B. H. Calhoun and A. Chandrakasan, "A 256kb sub-threshold SRAM in 65nm CMOS," IEEE ISSCC Dig. Tech. Papers., Feb. 2006, pp. 2592–2601.

- [2] L. Chang et al., "Stable SRAM cell design for the 32 nm node and beyond," in Symp. VLSI Technol. Circuits Dig. Tech. Papers, Jun. 2005, pp. 128–129.

- [3] K. Takeda et al., "A read-static-noise-margin-free SRAM cell for low- VDD and high-speed applications," IEEE J. Solid-State Circuits, vol. 41, no. 1, pp. 113–121, Jan. 2006. [4] T. Suzuki, H. Yamauchi, Y. Yamagami, K. Satomi, and H. Akamatsu, "A stable 2-port SRAM cell design against simultaneously read/write-disturbed accesses," IEEE J. Solid-State Circuits, vol. 43, no. 9, pp. 2109–2119, Sep. 2008.

- [5] L. Wen, Z. Li, and Y. Li, "Single-ended, robust 8T SRAM cell for low-voltage operation," Microelectron. J., vol. 44, no. 8, pp. 718–728, 2013.

- [6] M.-H. Tu et al., "A single-ended disturb-free 9T subthreshold SRAM with cross-point

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing," IEEE J. Solid-State Circuits, vol. 47, no. 6, pp. 1469–1482, Jun. 2012.

[7] B. Wang, T. Q. Nguyen, A. T. Do, J. Zhou, M. Je, and T. T. H. Kim, "Design of an ultralow voltage 9T SRAM with equalized bitline leakage and CAM-assisted energy efficiency improvement," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 62, no. 2, pp. 441–448, Feb. 2015.

[8] N. Maroof and B.-S. Kong, "10T SRAM using half-VDD precharge and row-wise dynamically powered read port for low switching power and ultralow RBL leakage," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 4, pp. 1193–1203, Apr. 2017. [9] S. Baeg, S. Wen, and R. Wong, "SRAM interleaving distance selection with a soft error failure model," IEEE Trans. Nucl. Sci., vol. 56, no. 4, pp. 2111–2118, Aug. 2009.

[10] I. J. Chang, J.-J. Kim, S. P. Park, and K. Roy, "A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS," IEEE J. Solid-State Circuits, vol. 44, no. 2, pp. 650–658, Feb. 2009.

[11] H. Noguchi et al., "Which is the best dualport SRAM in 45-nm process technology? – 8T, 10T single end, and 10T differential –," in Proc. IEEE Int. Conf. Integr. Circuit Design Technol. Tutorial, Jun. 2008, pp. 55–58.

[12] L. Wen et al., "Bit-interleaving-enabled 8T SRAM with shared dataaware write and reference-based sense amplifier," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 63, no. 7, pp. 643–647, Jul. 2016.