A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

# DESIGN OF EFFICIENT AREA STREAMING VIDEO ARCHITECTURE USING BRIEF DETECTOR

<sup>1</sup>B JYOTHI, <sup>2</sup>CH.GOPALA KRISHNA

<sup>1</sup>PG SCHOLAR, SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

<sup>2</sup>CH.GOPALA KRISHNA, ASSOCIATE PROFESSOR THE DEPARTMENT OF ECE IN SREE VAHINI INSTITUTE OF

SCIENCE & TECHNOLOGY

TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

#### **ABSTRACT:**

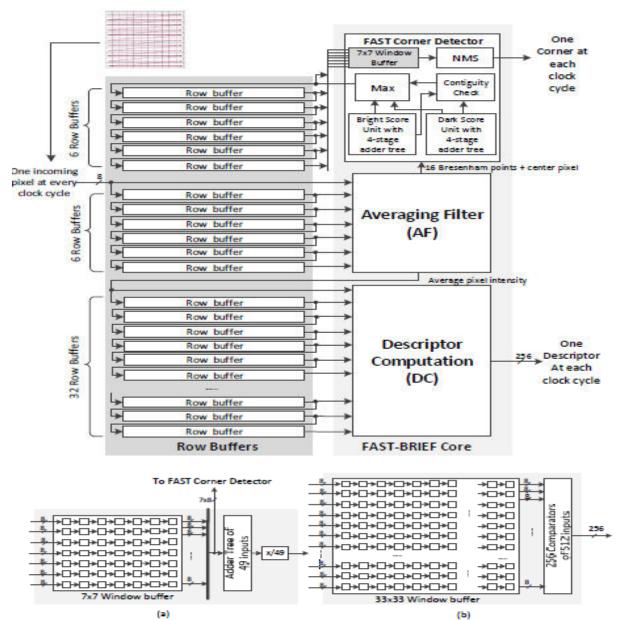

The blend of FAST corners and BRIEF descriptors give exceptionally powerful picture highlights. We present a novel finder for figuring the FAST-BRIEF highlights from streaming pictures. To lessen the intricacy of the BRIEF descriptor, we utilize a streamlined viper tree to perform summation by collection on streaming pixels for the smoothing activity. Since the window cushion utilized in existing plans for processing the BRIEF point-sets are regularly inadequately used, we propose an effective examining plan that adventures register reuse to limit the quantity of registers. Combination results dependent on 65-nm CMOS innovation show that the proposed FAST-BRIEF center accomplishes over 40% decrease in zone postpone item contrasted with the gauge plan. Moreover, we show that the proposed design can accomplish 1.4x higher throughput than the gauge engineering with somewhat lower energy utilization.

#### **INTRODUCTION:**

Unforgiving conditions, similar to space, are a test for electronic circuits when all is said in done and for recollections specifically. For example, radiation causes a few sorts of blunders that can disturb the circuitfunctionality [1]. One regular blunder for SRAM recollections is softerrors that change the estimation of at least one memory cells [2].To stay away from debasement in the information put away in mistake correctioncodes memory. (ECCs) are ordinarily utilized [3].ECCs add equality check pieces to every memory word to recognize and orrect mistakes. This

requires an encoder to register those pieces whenwriting to the memory and a decoder to recognize and address errorswhen perusing from the memory. These components increment the memoryarea and the force utilization, and can likewise decrease the accessspeed. These overheads increment with the blunder adjustment capability of the ECC. Customarily, codes that can address a solitary piece errorper word have been Specifically, utilized. single blunder adjustment doubleerror recognition (SEC-DED) codes that can likewise identify twofold errorsare regularly utilized [4]. As

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

of late, the quantity of mistakes that influence more than onememory cell has expanded altogether. This is expected to the scalingof the memory cells and is projected to become further [5]. Theseerrors, known as different cell disturbs (MCUs), represent a challengefor SEC-DED codes. One answer for guarantee that the MCU errorscan be rectified is to interleave the pieces of various legitimate wordsso that a MCU influences the slightest bit per word [6]. This is based onthe perception that the phones influenced by a MCU physicallyclose [7]. Interleaving, be that as it may, has an expense as it convolutes thememory plan [8]. In some space applications, there is an additionalissue as the quantity of mistakes is high, and SEC-DED codes may notbe adequate when blunders collect over the long haul [9]. These issues haveled to an expanded interest on the utilization of further developed ECCs SRAM memories.As toprotect **MCUs** influence cells that are near one another. various codesthat can address twofold nearby or significantly increase contiguous blunders have been recently proposed [8], [10]–[12]. These codes, by and large, do notrequire extra equality check bits and in the rest require only one ortwo extra pieces. The translating intricacy increments however in manycases can at present be executed with restricted effect on the memoryspeed. These codes are helpful for applications in which the blunder rateis low, nonetheless, when the mistake rate is huge, codes that can correcterrors on numerous autonomous pieces required are

[9].Research for multibit ECCs has zeroed in on diminishing the decodinglatency as much of the time, the conventional decoders are sequential andrequire a few clock cycles. Somewhat this should be possible forsome customary ECCs by utilizing an equal condition decoder [13] butthe decoder unpredictability detonates as the mistake rectification capacity orthe word size increments. Another methodology is to utilize codes that canbe decoded with low deferral, for example, symmetrical Latin squares (OLSs)or contrast set (DS) codes [14], [15]. On account of OLS codes, the fundamental issue is that they are not ideal regarding the number of equality check pieces and hence require more memory overhead. TheDS codes are more serious regarding equality check bits however arestill not ideal for some word lengths. For instance, the(21, 10) DS code can address 2cycle mistakes while a code with a similarblock size and code rate, and the (24,12) broadened Golay code [16]can right 3-digit blunders. Nonetheless, the Golay code requires a morecomplex decoder that needs a few clock cycles [17]. Namba et al. [18] have proposed a trade off arrangement forBose-Chaudhuri-Hocquenghem codes. The thought is that the mostcommon mistake designs are decoded in equal and the rest serially. In specific, single and twofold contiguous blunders are adjusted in asingle clock cycle. This implies that the most memory gets to canbe finished in a solitary clock cycle, and just a little rate ofthe words in mistake require a full sequential deciphering. This can empower

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

theuse of conventional ECCs that don't uphold quick equal interpreting toprotect SRAM recollections In this short, the utilization of the plan in [18] is considered for the(24,12) Golay code. In more detail, an effective equal decoder capableof rectifying the single and twofold neighboring blunders is presented. The decoder abuses properties of the Golay code to diminish theimplementation cost. This outcomes in a decoder that is more straightforward than a conventional SEC decoder however that can likewise address all twofold adjacenterrors and some triple-contiguous blunders. The proposed decoder has beenimplemented in equipment depiction language and planned to a 65-nm innovation to show its advantages. The principle commitment of thisbrief is to empower a quick and effective equal rectification of the singleand twofold contiguous mistakes in the (24,12) Golay code.

#### **RELATED WORK:**

ECCs add equality check pieces to every memory word to distinguish andcorrect mistakes. This requires an encoder to figure those pieces whenwriting to the memory and a decoder to recognize and address mistakes when perusing from the memory. These components increment the memoryarea and the force utilization, and can likewise decrease the accessspeed. These overheads increment with the mistake rectification capability of the ECC. Generally, codes that can address a solitary piece mistake for every word have been utilized. Specifically, single blunder rectification doubleerror

identification (SEC-DED) codes that can distinguish twofold likewise errorsare regularly utilized. The blend of FAST and BRIEF descriptors exceptionally powerful picture highlights. We present a novel identifier for registering the FAST-BRIEF highlights from streaming pictures. To decrease the unpredictability of the BRIEF descriptor, we utilize an improved snake tree to perform summation by aggregation on streaming pixels for the smoothing activity. Since the window cushion utilized in existing plans for figuring the BRIEF point-sets are regularly inadequately used, we propose an effective inspecting plan that adventures register reuse to limit the quantity of registers. Blend dependent on 65-nm results **CMOS** innovation show that the proposed FAST-BRIEF center accomplishes over 40% decrease in territory defer item contrasted with the pattern plan. Furthermore, we show proposed the engineering that accomplish 1.4x higher throughput than the standard design with somewhat lower energy utilization.

#### **EXPERIMENTAL RESULTS:**

The proposed design embraces similar computational squares and line cradles as appeared. Like the benchmark usage, another FAST corner and a 256-cycle BRIEF descriptor will be delivered at the pace of the approaching pixel. The FAST execution is equivalent to the gauge. Next, we portray the proposed plans for AF and DC. The benchmark and proposed designs were actualized utilizing Verilog and

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

orchestrated with Synopsys DC focusing on the 65-nm CMOS innovation library. The plans were combined to accomplish most extreme clock recurrence. shows the zone defer union outcomes for the benchmark and proposed AF and DC modules. The region usage of the proposed AF module is about 36% lower than the standard AF. Also, as examined in the past area, the basic way deferral of the gauge AF is administered by the inertness of the divider, which is bigger than the basic way deferral of the proposed AF (for example dormancy of one viper). The benchmark DC usage for GI - GIV BRIEF point pair designs have comparable basic way deferral and territory usage. This is normal as the gauge DC configuration is the same for all the designs. The basic way postponement of the benchmark and proposed DC is comparable as they are both administered by the inactivity of the comparator. In any case, in contrast to the standard usage, the proposed DC shows contrasting zone usage for the different BRIEF point-pair setups. These outcomes are predictable with our asset investigation, where the territory usage of Proposed-DC-GI is marginally higher than the gauge DC, however for the remainder of the BRIEF point pair arrangements, we can notice a huge decrease in region usage. The proposed

DC usage for GI - GIV BRIEF point-pair arrangements accomplishes - 2.5%, 20.4%, 30%, also, 17.4% territory decrease when contrasted with the relating benchmark usage. These outcomes unmistakably show the adequacy of the proposed pipelining approach for DC. reports the union outcomes for the FAST-BRIEF center (FAST, AF and DC) of the gauge and proposed plans. It very well may be seen the proposed configuration that accomplishes a normal decrease of 17% in zone use over the standard plan. The last section of Table 4 shows the rate Area-Delay Item (ADP) decrease of the proposed FAST-BRIEF center over the gauge. By and large, the ADP decrease of the proposed plan over the benchmark configuration is over 40%. the force utilization and energy per pixel of the gauge and proposed streaming FAST-BRIEF engineering for 640x480 pictures. This requires 44 column supports, where the size of each line cushion is 640. Energy per pixel is processed as the result of intensity (mW) and least clock period (ns). In spite of the fact that the force utilization of the benchmark design is lower than the proposed (because of the lower working recurrence), the energy per pixel of the two designs have peripheral contrast.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

Fig. 3(a). Averaging filter (AF) of the baseline implementation, (b) Descriptor computation (DC) of the baseline implementation.

The quantity of registers needed by the proposed DC for the model is around 23 (standardized to 8-digit registers) contrasted with 64 which is needed by the gauge DC. It is clear that the proposed configuration can prompt fundamentally lower number of

registers, anyway this relies upon the arrangement of the BRIEF point-sets. In particular, the quantity of required move registers relies upon n (size of the descriptor), the aggregate section counterbalances between the BRIEF point

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

sets, and the open doors for register sharing. Furthermore, the quantity of touch shifters relies upon n and the distance of s or d from the furthest left section of the picture fix. We will show that the proposed DC prompts eminently lesser zone usage by and large.

#### **ONCLUSION:**

The proposed FAST-BRIEF engineering consolidates equipment advancements for the smoothing activities and parallel trial of the BRIEF point sets. A tale pipelining approach was acquainted with register the double trial of numerous BRIEF point sets from every approaching pixel, and afterward utilizing bit shifters to synchronize the yields of the BRIEF descriptors. The proposed configuration accomplishes huge territory deferral and throughput benefits over the traditional plan.

#### **REFERENCES:**

- [1] S. Gauglitz, T. Hollerer, and M. Turk, "Evaluation of interest point detectors and feature descriptors for visual tracking", *International Journal of Computer Vision*, Vol. 94, pp. 335-360, 2011.

- [2] J. Soh and X. Wu, "An FPGA-Based Unscented Kalman Filter for System-On-Chip Applications", *IEEE Transactions on Circuits and Systems II*, Vol. 64, No. 4, pp. 447-451, April 2017.

- [3] M. Calonder, V. Lepetit, C. Strecha, and P. Fua, "BRIEF: Binary Robust Independent Elementary Features", *European Conference o Computer Vision*, pp. 778-792, 2010.

- [4] M. Calonder, V. Lepetit, M. Ozuysal, T. Trzcinski, C. Strecha, and P. Fua, "BRIEF:

- Computing a Local Binary Descriptor Very Fast", IEEE Transactions on Pattern Analysis and Machine Intelligence, Vol. 34, No. 7, July 2012, pp. 1281-1298.

- [5] R. Mur-Artal, J.M.M. Montiel, and J.D. Tardos, "ORB-SLAM: A Versatile and Accurate Monocular SLAM System", *IEEE Transactions*

- on Robotics, Vol. 31, No. 5, October 2015, pp. 1147-1163

- [6] H. Heo, J.-Y. Lee, K.-Y. Lee, and C.-H. Lee, "FPGA-based Implementation of FAST and BRIEF Algorithm for Object Recognition", IEEE TENCON, 2013.

- [7] C.-S. Seo, S.-Y. Kim, J.-P. Ko, H.-J. Chung, Y.-H. Lee, "Feature Point Detection Hardware Based on Fast and Brief Algorithm", International Journal of Management and Applied Science (IJMAS), Vol. 3, No. 1, 2015, pp. 81-84.

- [8] J.S. Park, H.E. Kim, and L.S. Kim, "A 182mW 94.3 f/s in full HD patternmatching based image recognition accelerator for an embedded vision system in 0.13-µm CMOS technology", *IEEE Trans. Circuits and Systems for Video Technology*, Vol. 23, No. 5, pp. 832-845, 2013

- [9] W. Farhat, H. Faiedh, and C. Souani, "Real-time Embedded System for Traffic Sign Recognition based on ZedBoard", Journal of Real-Time Image Processing, April 2017, pp. 1-11.

- [10] M. Fularz, M. Kraft, A. Schmidt and A. Kasinski, "A High-Performance FPGA-based Image Feature Detector and Matcher based on the FAST and BRIEF Algorithms",

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

International Journal of Advanced Robotic Systems, Vol. 12, 2015.

[11] F. Brenot, J. Piat, and P. Fillatreau, "FPGA-based Hardware Acceleration of a BRIEF Correlator Module for a Monocular SLAM Application", Proceedings of the 10th International Conference on Distributed Smart

Camera, 2016, pp. 184-189.

[12] W. Fang, Y. Zhang, B. Yu, and S. Liu, "FPGA-based ORB Feature Extraction for Real-Time Visual SLAM", Available: https://arxiv.org/abs/1710.07312.

[13] R. de Lima, J. M-Carranza, A. M-Reyes, and R. Cumplido, "Improving the Construction of ORB through FPGA-based Acceleration", *Machine Vision and Applications*, Vol. 28, pp. 525-537.

### **Student Details:**

B Jyothi ,M.Tech SreeVahini Institute of Science & Technology.

#### **Guide Details:**

Ch.Gopala Krishna, Associate Professor of the Department of ECE, in SreeVahini Institute of Science & Technology.