A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

## Modified High Speed 32-bit Vedic Multiplier Design and Implementation

<sup>1</sup>**VEMU BHANU PRASAD,** <sup>2</sup>**B SAMBASIVA RAO** <sup>1</sup>Student, <sup>2</sup>Asst. Professor <sup>1,2</sup>DJR COLLEGE OF ENGINEERING & TECHNOLOGY

#### ABSTRACT

The proposed research work specifies the modified version of binary vedic multiplier using vedic sutras of ancient vedic mathematics. It provides modification in preliminarily implemented vedic multiplier. The modified binary vedic multiplier is preferable has shown improvement in the terms of the time delay and also device utilization. The proposed technique was designed using kogge stone adderand implemented in Verilog HDL. For HDL simulation, xilinx tool is used and for circuit synthesis, Xilinx is used. The simulation has been done for 4 bit, 8 bit, 16 bit, 32 bit multiplication operation. Only for 32 bit binary vedic multiplier technique the simulation results are shown. This modified multiplication technique is extended for larger sizes.

Index Terms-Vedic multiplier, Kogge stone adder, Verilog HDL, simulation, synthesis.

## **1. INTRODUCTION**

Multipliers play an important role in today's digital signal processing and various other applications. With advances in technology, many researchers have tried and are trying to design multipliers which offer either of the following design targets – high speed, low power consumption, regularity of layout and hence less area or even combination of them in one multiplier thus making them suitable for various high speed, low power and compact VLSI implementation.

The common multiplication method is "add and shift" algorithm. In parallel multipliers number of partial products to be added is the main parameter that determines the performance of the multiplier. To reduce the number of partial products to be added, vedic multiplier using carry look ahead adder is one of the most popular Urdhva Tiryakbhayam method. In this lecture we introduce the multiplication algorithms and architecture and compare them in terms of speed, area, power and combination of these metrics.

Vedic Mathematics is one of the most ancient methodologies used by the Aryans in order to

perform mathematical calculations. This consists of algorithms that can boil down large arithmetic operations to simple mind calculations. The above said advantage stems from the fact that Vedic mathematics approach is totally different and considered very close to the way a human mind works. The efforts put by Jagadguru Swami Sri Bharati Krishna Tirtha Maharaja to introduce Vedic Mathematics to the commoners as well as streamline Vedic Algorithms into 16 categories or Sutras needs to be acknowledged and appreciated. Urdhva Tiryakbhayam is one such The multiplication algorithm which is well known for its efficiency in reducing the calculations involved.

With the advancement in the VLSI technology, there is an ever increasing quench for portable and embedded Digital Signal Processing (DSP) systems. DSP is omnipresent in almost every engineering discipline. Faster additions and multiplications are the order of the day. Multiplication is the most basic and frequently used operations in a CPU. Multiplication is an operation of scaling one number by another.

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

Multiplication operations also form the basis for other complex operations such as convolution, Discrete Fourier Transform, Fast Fourier Transforms, etc. With ever increasing need for faster clock frequency it becomes imperative to have faster arithmetic unit. Therefore, DSP engineers are constantly looking for new algorithms and hardware to implement them. Vedic mathematics can be aptly employed here to perform multiplication.

## 2. LITERATURE SURVEY

Vijay kumar reddy Modified High Speed Vedic Multiplier Design and Implementation The proposed research work specifies the modified version of binary vedic multiplier using vedic sutras of ancient vedic mathematics.It provides modification in preliminarilry implemented vedic multiplier. The modified binary vedic multiplier is preferable has shown improvement in the terms of the time delay and also device utilization. The technique proposed was designed and implemented in Verilog HDL.For HDL simulation, modelsim tool is used and for circuit synthesis, Xilinx is used. The simulation has been done for 4 bit, 8 bit,16 bit, multiplication operation. Only for 16 bit binary vedic multiplier technique the simulation results are shown. This modified multiplication technique is extended for larger sizes. The outcomes of this multiplication technique is compared with existing vedic multiplier techniques.

C. Liu, J. Han, and F. Lombardi, "A Low-Power, High-Performance Multiplier with Configurable Partial Error Recovery", Proc. of IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE), [Approximate circuits have been considered for error-tolerant applications that can tolerate some loss of accuracy with improved performance and energy efficiency. Multipliers are key arithmetic circuits in many such applications such as digital signal processing (DSP). In this paper, a novel multiplier with a lower power consumption and a shorter critical path than traditional multipliers is proposed for highperformance DSP applications. This multiplier leverages a newly-designed approximate adder that limits its carry propagation to the nearest neighbors for fast partial product accumulation. Different levels of accuracy can be achieved through a configurable error recovery by using different numbers of most significant bits (MSBs) for error reduction. The multiplier has a low mean error distance, i.e., most of the errors are not significant in magnitude. Compared to the Wallace multiplier, a 16-bit multiplier implemented in a 28nm CMOS process shows a reduction in delay and power of 20% and up to 69%, respectively. It is shown that by utilizing an appropriate error recovery, the proposed multiplier achieves similar processing accuracy as traditional exact multipliers but with significant improvements in power and performance.

#### 3. PROPOSED VEDIC MULTIPLIER

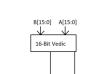

A binary multiplier can be used in digital electronics as a electronic circuit, such as in of two binary computers to find the product numbers.Carbon-copy of normal multiplicationtechnique is used by binary multiplier, the multiplicand is multiplied with each bit of the multiplier beginning from the least significant bit. Two half adder(HA) modules can be used in order to implement a 2-bit binary multiplier.A no of com- puter arithmetic calculations can be used to appliance digital multiplier. Among these techniques many imply computing a set of partial products, and then summing the generated partial products together.Fig. 1, shows 2x2 binary multiplier.

Fig 1: 2bit binary multiplier

The mode used by Vedic multiplier is Vedic mathematics. By using this technique it will

A peer reviewed international journal

www.ijarst.in

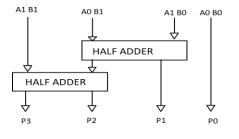

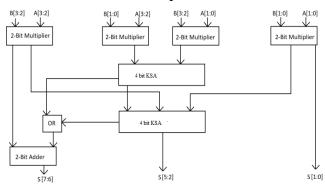

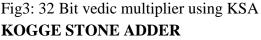

consumes fewer hardware increase. and elements. The sutra used by Vedic multiplier is Urdhva Tiryakbhyam which means Vertically as well as Crosswise. The Fig. 3 shows block diagram of 32 bit vedic multiplier circuit. The2 input bits are separated into 2 similar parts the vertical and cross product calculations can be done as shown in Fig. 3, with inputs A[31:0] and B[31:0]. As shown in the Fig. 3, the 2 adders are used in the design of intermediate stages of the addition. The output carry Cout from these two adders is given as input to another KSA. If bits are not of equal sizes concatenate them.For 32-bit Modified Vedic multiplier the outputs of parallel adder is given to OR gate and of the size of last KSA is reduced to half. Fig. 3, shows 32-bit Vedic multiplier.

Fig2: 4 Bit vedic multiplier using KSA

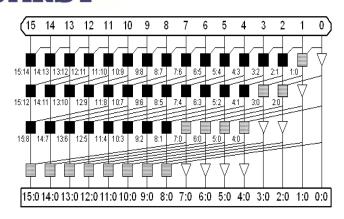

KSA is a parallel prefix form carry look ahead adder. It generates carry in O (logn) time and is widely considered as the fastest adder and is widely used in the industry for high performance arithmetic circuits. In KSA, carries are computed fast by computing them in parallel at the costof increased area. The complete functioning of KSA can be easily comprehended by analyzing It in terms of three distinct parts :

1. Preprocessing : This step involves computation of generate and propagate signals corresponding too each pair of bits in A and B.

pi = Ai xor Bi

gi = Ai and Bi

2 . Carry generation network: This block differentiates KSA from other adders and is the main force behind its high performance. This step involves computation of carries corresponding to each bit. It uses group propagate and generate as intermediate signals. Pi:j = Pi:k+1 and Pk:j

Gi: j = Gi: k+1 or (Pi: k+1 and Gk: j)

3. Post processing: This is the final step and is common to all adders of this family (carry look ahead). It involves computation of sum bits.

Si = pi xor Ci-1

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

## Fig 4: 16 bit kogge stone adder

# Fig 5:Complex logic cells inside the Prefix Carry Tree

## 4. **RESULTS**

RTL SCHEMATIC: The RTL schematic is abbreviated as the register transfer level it denotes the blue print of the architecture and is used to verify the designed architecture to the ideal architecture that we are in need of development .The hdl language is used to convert the description or summery of the architecture to the working summery by use of the coding language i.e verilog ,vhdl. The RTL schematic even specifies the internal connection blocks for better analyzing .The figure represented below shows the RTL schematic diagram of the designed architecture.

Fig6: RTL Schematic of Vedic multiplier using KSA

TECHNOLOGY SCHEMATIC:- The technology schematic makes the representation of the architecture in the LUT format ,where the LUT is consider as the parameter of area that is used in VLSI to estimate the architecture design .the LUT is consider as an square unit the memory allocation of the code is represented in there LUT s in FPGA.

Fig 7: View Technology Schematic of Vedic multiplier using KSA

SIMULATION: The simulation is the process which is termed as the final verification in respect to its working whereas the schematic is the verification of the connections and blocks. The simulation window is launched as shifting from implantation to the simulation on the home screen of the tool and the simulation window confines

A peer reviewed international journal

#### www.ijarst.in

#### ISSN: 2457-0362

the output in the form of the wave forms. Here it has the flexibility of providing the different radix number systems.

Fig 8:Simulated Waveforms of Vedic multiplier using KSA

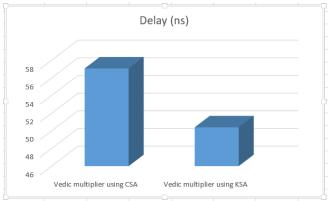

PARAMETERS: Consider in VLSI the parameters treated are area,delay and power ,based on these parameters one can judge the one architecture to other. Here the consideration of delay is considered the parameter is obtained by using the tool XILINX 14.7 and the HDL language is verilog language.

| Parameter  | Vedic multiplier using CSA | Vedic multiplier using KSA |

|------------|----------------------------|----------------------------|

| Delay (ns) | 57.067                     | 50.401                     |

## CONCLUSION

This paper has presented a systematic method for binary multiplier circuits which is based on Vedic mathematics. When it comes to the terms of time delay then the proposed system is more efficient than exisitng methods. Elongation for a higher bit size can be done with help of proposed technique. Moreover, adders of different architectures can be used in the kogge Stone Adder design used in the proposed modified Vedic multiplier. Among many techniques modified architecture is used to increase and speed up the multiplication and the design was synthesized and simulated using Xilinx 14.7 ise design suit.

## REFERENCES

- [1] S. Akhter, "VHDL implementation of fast NxN multiplier based on Vedic mathematics," in Proc. 18th European Conference on Circuit Theory and Design, 2007, pp. 472-475

- [2] S. Nagaraj, Dr.G.M. Sreerama Reddy and Dr.S. Aruna Mastani; A Comparative Study on Different Multipliers-SurveyJournal of Advanced Research in Dynamical and Control Systems14739-7522018Institute of Advanced Scientific Research.

- [3] M.Pushpa, S. Nagaraj, Design and Analysis of 8-bit Array, Carry Save Array, Braun,Wallace Tree and Vedic Multipliers, IEEE Sponsored International Conference On New Trends In Engineering & Technology(ICNTET 2018).

- [4] Nagaraj, S; Thyagarajan, K; Srihari, D; Gopi,

K; Design and Analysis of Wallace Tree

Multiplier for CMOS and CPL Logic2018

International Conference on Computation of

Power, Energy, Information and Communication (ICCPEIC)006-0102018IEEE

- [5] Josmin Thomas ; R. Pushpangadan ; S Jinesh Comparative study of performance Vedic multiplier on the Basis of Adders used 2015

IEEE International WIE Conference on Electrical and Computer Engineering (WIECON-ECE)

- [6] S. Nagaraj, Dr.G.M. Sreerama Reddy and Dr.S. Aruna Mastani; A Survey on Adiabatic

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

LogicInternational Conference on Communications, Signal Processing and VLSI(IC2SV2019),Springer Conference ,National Institute of Technology, Warangal.

- [7] S. Nagaraj,K.Venkataramana Reddy and and P.Anil Kumar3i;Analysis of Vedic Multiplier for Conventional CMOS & Complementary Pass Transistor Logic(CPL) Logics SCOPUS Indexed Springer 8th Interna- tional Conference on Innovations in Electronics and Communication Engineering, (ICIECE-2019).

- [8] Au L.S. and Burgess N. (2002), "A (4:2) adder for unified GF(p) and GF(2n) Galois field Multipliers", Proceedings of 36th IEEE Asilomar Conference on Signals, Systems, and Computers, vol. 2, pp. 1619-1623.

- [9] Chittibabu A., Sola V.K. and Raj C.P. (2006), "ASIC Implementation of New Architecture for constant coefficient Dadda multiplier for High- Speed DSP applications", Proceedings of the National Conference on Recent trends in Electrical, Electronics and Computer Engineering, JCECON, pp. 299 304.

- [10] Ramesh Pushpangadana, Vineeth Sukumarana, Rino Innocenta, Dinesh Sasikumara & Vaisak Sundara,"High Speed Vedic Multiplier Digital Signal for Processors", IETE **JOURNAL** OF RESEARCH, Vol 55, ISSUE 6, NOV-DEC 2009

- [11] Kumar, M SATHISH; Nagaraj, S; The campus security tracking system based on RFID and Zigbee networkInt. J. Smart Sensors Ad Hoc Netw.

- [12] Nagaraj, S; Reddy, R Mallikarjuna; FPGA Implementation of Modified Booth Multiplier, International Journal of Engineering Research and Applications (IJERA),ISSN: 2248-9622, Vol. 3, Issue 2,