A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

# PERFORMANCE EVALUATION OF 10T SRAM CELL STRUCTURES BY USING ADIABATIC SWITCHING TECHNIQUES

<sup>1</sup>P.B.L. K MARUTHI, <sup>2</sup>K. VENKANNA

<sup>1</sup>PG SCHOLAR, SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

<sup>2</sup>ASSOCIATE PROFESSORTHE DEPARTMENT OF ECE IN SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

#### **ABSTRACT:**

Force utilization, postponement, and spillage current are the significant plan worry of CMOS Technology. Particularly for short channel gadgets, the issue of spillage power is more articulated. Notwithstanding that, as the innovation packs, the spillage current additionally increments exceptionally quick. Accordingly, various low force methods have been advancing to decrease the spillage current in CMOS innovation. Due to innovation progressions, SRAM cell size is diminishing, the spillage current and force become the huge segments to bargain with. In this paper, we are proposing different SRAM plan strategies for 6T, 8T and 10T models; one is by thinking about innovation varieties. For that, traditional SRAM cell is planned utilizing 120 and 90nm advances also, looked at their parametric varieties. The other plan part of SRAM is, utilizing rationale plan procedures, for example, Pass Semiconductors rationale, Transmission entryway rationale and adiabatic rationale. The presentation of each SRAM configuration is contrasted and regular SRAM as far as deferral, force and zone. We seen that for low force applications one could incline toward adiabatic rationale to CMOS rationale. The Transmission door SRAM appropriate for low spillage current applications, Pass Semiconductor Logic is appropriate for the plans where basic way and region are to be low. List Terms: 6T, 8T and 10T SRAM arrangements, parametric varieties, rationale plan strategies, delay, power, spillage current, Pass Transistors rationale, Transmission entryway rationale and adiabatic rationale.

#### INTRODUCTION:

As indicated by International Technology Guide for Semiconductor (ITRS) reports the present size of 6T SRAM cell 0.096 µm2 may become 0.003 µm2 before the finish of 2028 on the

ilicon territory with a normal size decrease of 38.8% for at regular intervals [1]. This shows a rising interest for additional chips territory for inserted memory with a responsibility for low

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

information force. reserve maintenance. strength, and less cell egion. SRAM assumes a basic part in present day chip framework, convenient gadgets like PDA, mobile phones, convenient mixed media gadgets and in SoC's. SRAM based reserve recollections are regularly used to accomplish higher speed processor. The pattern of scaling of gadget brings a few difficulties like force dispersal, sub limit spillage, turn around diode spillage, also, strength. From few years, CMOS gadgets are downsized to arrive at the better execution regarding pace, size and dependability, power dispersal. Decrease in the edge voltage and the door oxide thickness are the main driver for the development of many progressed research advancements of SRAM plans. The possible boundaries that show sway on execution of SRAM memory considered are natural boundary variance, arbitrary dopants variance, oxides thickness change, and line edge unpleasantness debase the strength of SRAM cells. Since the ordinary 6T SRAM experiences security issues, an exertion is being made to tackle utilizing Schmitt trigger based SRAM plan in [2] shows substantially less force than the current, yet at expense of expanded number semiconductors. Be that as it may, this strategy power dissemination alongside dependability upgrades. There are different strategies [3] such as adjusted plan for charge partaking in which peruse release power is

reused to lessen low swing on peruse and compose lines to target decrease in force scattering. Utilizing less number semiconductors simultaneously great read security is accomplished by actualizing the 7T SRAM plan [4], which diminishes zone and power. Charge sharing method is presented in executing 8T [5, 6], 10T SRAM to lessen power utilization, with less number of semiconductors [7, 8], which brings about decrease of power. In [9], distinctive SRAM plans, for example, 6T, 8T, and 10T were tended to dependent on various rationales to improve soundness with low force and region as significant concerns. power and region. It is seen that for low force applications one can lean toward adiabatic rationale to CMOS rationale. The Transmission entryway SRAM appropriate for low spillage current applications, Pass Transistor Logic is appropriate for the plans where basic way and region are to be low. The proposed plans were actualized in Microwind 3.1. The remainder of the paper is coordinated as follows: Different SRAM cell arrangements for example 6T, 8T, and 10T are talked about in area II. Area III gives the subtleties of proposed work. Area IV gives execution correlation regarding power scattering and greatest current region and deferral for different kinds of SRAM setups against the innovation varieties and dependent on rationale plan. Ends and future work are given in segment.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

**RELATED WORK:**

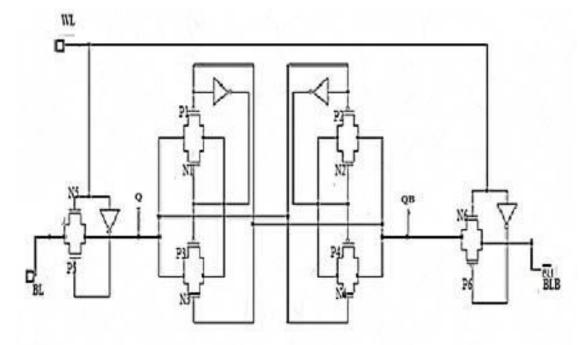

A. Audit Stage The most generally utilized arrangements in SRAM configuration are 6T[1], 8T[5] and 10T[7]. Poor solidness, little hold, and read static clamor edges are the regularly observed issues in 6T. Particularly in read activity, the weakness in solidness will happen and is predominantly due to the voltage division among access and driver semiconductor. This issue was tended to by utilizing 8T structure in which the information holding component what's more, information yield component were independently taken. Accordingly read '1' esteem because of not having any release way. Be that as it may, the issue is with peruse current stream to ground. Development of 10T kills this issue by utilizing two more semiconductors in the decoupled read way. Rather than depleting the read current to ground, the read wayis associated with BL and BLB through these 2 semiconductors.

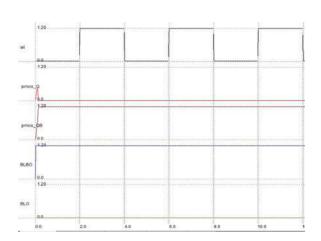

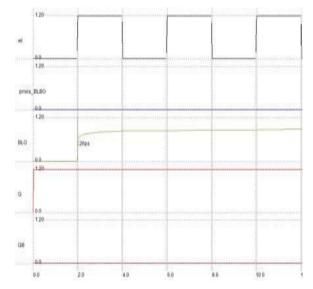

### **EXPERIMENTAL RESULTS:**

The proposed work is expected to arrive at plan of low force SRAM. Dynamic force fluctuates as VDD2. So decreasing the stock voltage diminishes power dissemination [10]. Particular recurrence decrease method and multi-limit voltage methods are not many, which decreases dynamic power just as spillage power at framework level.

Semiconductor resizing can be utilized to accelerate circuit and diminishes power. Utilizing this method, SRAM is planned in 120nm and 90nm with decrease of voltage. Notwithstanding, seen that resizing semiconductor with diminished supply voltage influences circuit speed and is the significant inadequacy of this methodology. Thus, rather than innovative arrangements, rationale plan as an answer is executed that experienced the issue of circuit execution debasement presented by decrease of voltage. A portion of the rationale methods utilized as low force plans are rest semiconductors to decrease reserve power, parallelism and pipelining in framework engineering, clock crippling, shut down of chosen rationale blocks, adiabatic registering. In the proposed work, SRAM is planned utilizing Transmission entryway, pass semiconductor and adiabatic rationale. Results are caught for each plan and the presentation of SRAM is analyzed in wording of basic way delay, power dissemination, most extreme current and area.A transmission door is a switch involved a pMOS semiconductor and nMOS semiconductor, which will specifically block or outperform a sign leve from the contribution to the yield. The one-sided control doors are utilized to keep up both the semiconductors are in either on or off. The traditional SRAM is actualized utilizing TG

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

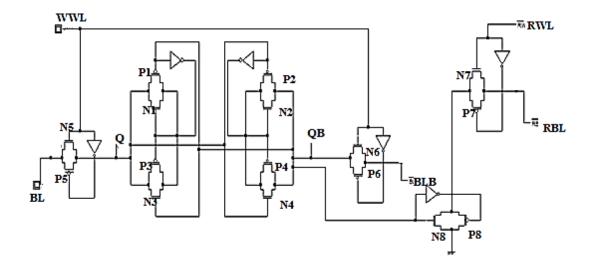

rationale and the subsequent 6TG SRAM cell is appeared in Fig. 1. Transmission entryways are used in the spot of two cross-coupled inverters. Two more TG cells are utilized in the spot of access semiconductors. The control

signal, indicated by WL, is associated with the Access TG cells, so that, the information can be composed or perused from bit lines comparable to traditional SRAM cell.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

#### **CONCLUSION:**

We zeroed in on the plan of SRAM cell against the varieties of innovation boundaries for example, power dissemination, delay, greatest current and region. We have planned the 6T; 8T and 10T SRAM cells utilizing semiconductor resizing method with advancements 120nm and 90nm furthermore, saw that as innovation contracts zone, power dissemination and greatest current required likewise shrivels however at the punishment of expanded postponement. Utilizing transmission entryway, semiconductor rationale and adiabatic rationale, we have planned underlying models of 6T, 8T and 10T SRAM cells in 120nm innovation and noticed the execution of each plan regarding power dissemination, greatest current, basic way delay also, territory. From the perceptions it is

noticed that region and basic way delay are decreased when pass semiconductor rationale is utilized contrasted with that of both customary CMOS rationale and transmission door rationale. Force dissemination and zone are diminished when conventional CMOS rationale utilized contrasted with that of transmission door rationale Contrasting with all rationales, adiabatic rationale results in low force

#### .REFERENCES:

[1] M. Parvathi, K. Satya Prasad, N. Vasantha, "Testing of Embedded SRAMs using Parasitic Extraction Method", Robotic, Vision, Signal Processing and Power Applications (ROVISP), Empowering Research and Innovation, ISBN 978-981-10-1721-6, Springer LNEE, 2016, pp:47-61.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

[2] Sai Silpa. Chandavolu, K. Amarnath, "Improved Stability SRAM Design for Low power Applications", International Journal of Application or Innovation in Engineering & Management (IJAIEM), ISSN 2319 - 4847, Volume 3, Issue 10, October 2014, pp:185-189. [3] Anu Tonk, Meenu Rani Garg, "Study Of SRAM and Its Low Power Techniques", International Journal of Electronics Communication Engineering & Technology, ISSN 0976 - 6464, Volume 6, Issue 2, February (2015), pp. 35-43.

Shyam Ankit [4] Akashe, Srivastava, SanjaySharma, "Calculation of PowerConsumption in 7 Transistor SRAM Cellusing Cadence Tool", International Journalof Advances Engineering in TechnologyIIJEAT), Sept 2011, ISSN: 2231-1963, Vol.1, Issue 4, pp. 189-194.

[5] Nahid Rahman, B. P. Singh, "Design AndVerification Of Low Power SRAM Using8T SRAM Cell Approach", International Journal Of Computer Applications (0975-8887) April 2013, Volume 67- No.18.

[6] Ch.Saibabu, Sagar Krishna Sivvam,"Modified 8T Design of Charge SharingTechnique for Dynamic Power Reduction",August 2014, Volume.3, issue 8.

[7] Ramkumar R, Jasmin M, "A low Voltage10-T SRAM cell with Inbuilt Charge Sharingfor Dynamic Power Reduction", SocialScience research network, Feb-2014,pp:1-4.

[8] Ankush Jaiswal, M. B Mali, "Low power 10TSRAM design for dynamic powerreduction", International Journal of Innovative Research in Science Engineering and Technology, June 2015 volume 4, Issue 6.

R. K. Sah, I. Hussain, M. Kumar,"Performance Comparison for **DifferentConfigurations** of **SRAM** Cells",International Journal of Innovative Researchin Science. Engineering and Technology, January 2015. Vol. 4, Issue 1.

[10]M. Parvathi, N. Vasantha, K. Satya Prasad, "Design of High Speed Low Power HighAccurate (HS-LP-HA) Adder", International Journal of Computer and Communication Engineering (IJCCE), ISSN: 2010-3743, pp:547-550.

### **Student Details:**

P.B.L. K MARUTHI,M.Tech SreeVahini Institute of Science & Technology.

#### **Guide Details:**

K Venkanna , Associate Professor of the Department of ECE, in SreeVahini Institute of Science & Technology

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in