A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

# Efficient Pipelined FIR Filter Design: Unlocking Block Processing in Transpose Form Configuration

Shiva Parvathi<sup>1</sup>, G. Lekhana<sup>2</sup>, Harshavardhini Botla<sup>2</sup>, J. Panitha<sup>2</sup>, K. Divya<sup>2</sup>

<sup>1</sup> Department of ECE, Mallareddy Engineering College for Women, (UGC-Autonomous), Hyderabad, India, smitamrecw@gmail.com.

#### **Abstract**

This paper introduces a groundbreaking approach to designing high-speed pipelined Finite Impulse Response (FIR) filters by harnessing the potential of transpose form configuration. Traditionally, transpose form FIR filters excel in multiple constant multiplications (MCM), yielding substantial computational savings. However, they have not been readily compatible with block processing, unlike direct form configurations. Our research breaks new ground by demonstrating the feasibility of implementing block FIR filters within the transpose form configuration, offering enhanced area-delay efficiency for large-order FIR filters in both fixed and reconfigurable applications. Through meticulous critical path analysis, we present a meticulously optimized flow graph tailored for transpose form block FIR filters, minimizing register complexity. We introduce a versatile block formulation technique and propose a novel multiplier-based architecture suitable for reconfigurable applications. Additionally, we unveil a low-complexity design leveraging the MCM scheme for efficient block implementation of fixed FIR filters. This innovative approach promises significant advancements in high-speed FIR filter design, paving the way for improved performance in various signal processing applications.

**Keywords**: Pipelined FIR Filter, Transpose Form Configuration, Block Processing, Multiple Constant Multiplications (MCM), Area-Delay Efficiency, Reconfigurable Architecture.

#### 1. Introduction

Finite-impulse response (FIR) advanced channel is broadly utilized in a few computerized flag handling applications, for example, discourse preparing, noisy speaker leveling, reverberate scratchoff, versatile clamor scratch-off, and different correspondence applications, including programming characterized radio (SDR) et cetera [1]. A significant number of these applications require FIR channels of vast request to meet the stringent recurrence details [2]–[4]. All the time these channels need to help high inspecting rate for fast computerized correspondence [5]. The quantity of duplications and augmentations required for each channel yield, be that as it may, increments directly with the channel arrange. Since there is no excess calculation accessible in the FIR channel calculation, ongoing execution of an extensive request FIR channel in an asset obliged condition is a testing undertaking. Channel coefficients all the time stay steady and known from the earlier in flag preparing applications. This component has been used to lessen the multifaceted nature of acknowledgment of augmentations. A few plans have been proposed by different specialists for effective acknowledgment of FIR channels (having settled coefficients) utilizing circulated math [18] and various steady augmentation techniques [7], [11]-[13]. DA-based structures utilize query tables to store precomputed results to diminish the computational unpredictability. The MCM strategy then again diminishes the quantity of increases required for the acknowledgment of duplications by regular sub articulation sharing, when a given info is increased with an arrangement of constants. The MCM plot is more viable, when a typical operand is increased with a greater number of constants.

<sup>&</sup>lt;sup>2</sup> Student, Department of ECE, Mallareddy Engineering College for Women, (UGC-Autonomous), Hyderabad, India.

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

Accordingly, the MCM plot is reasonable for the execution of huge request FIR channels with settled coefficients. However, MCM squares can be shaped just in the transpose frame design of FIR channels.

### 2. Implementation of Wallace Tree Multiplier

Wallace Trees are combinatorial logic circuits used to multiply binary integers. Developed utilizing full adders and half adders, they are a quick, effective technique to actualize increase. Since these adders don't proliferate convey values between bits, they are quicker than parallel adders and can deliver augmentation items quicker than other duplication equipment. Whole number augmentation can be performed utilizing any of a few techniques. The conventional move include approach and ROM query tables are two techniques used to actualize duplication, however every ha its disadvantages. The time expected to figure items utilizing the move include strategy increments straightly as the quantity of bits in the operands increments, and the measure of the query ROM increments exponentially with increments in the extent of the operands. The advantage of the Wallace tree is that there are just O (log n) decrease layers, and each layer has O (1) proliferation delay. As making the halfway items is O (1) and the last expansion is O (log n), the duplication is just O (log n), very little slower than expansion (be that as it may, considerably more costly in the entryway tally). Gullibly including incomplete items with normal adders would require O (log2 n) time. From an unpredictability theoretic viewpoint, the Wallace tree calculation places augmentation in the class NC. The figure underneath shows how a Wallace Tree Multiplier can be acknowledged for the 8-bit i.e. an 8x8 multiplier.

Fig.1 Example of reduction on 8x8 multiplier

#### 3. MCM Based FIR Filter

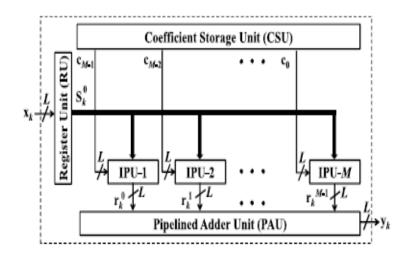

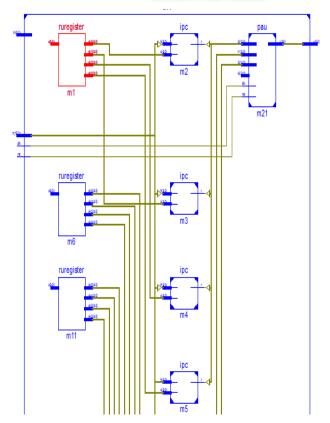

The proposed structure for square FIR channel is [based on the repeat connection of (12)] appeared in Fig. 2 for the square size L=4. It comprises of one coefficient selection unit (CSU), one register unit (RU), M number of inner product units (IPUs), and one pipeline adder unit (PAU). The CSU stores coefficients of the considerable number of channels to be utilized for the reconfigurable application. It is actualized utilizing N ROM LUTs, to such an extent that channel coefficients of a specific direct channel are acquired in one clock cycle, where N is the channel length. The RU [shown in Fig. 7(a)] gets xk amid the kth cycle and creates L lines of S0k in parallel. L lines of S0kare transmitted to M IPUs of the proposed structure. The M IPUs likewise get M short-weight vectors from the CSU with the end goal that amid the kth cycle, the (m+1) th IPU gets the weight vector cM-m-1 from the CSU and L lines of S0k frame the RU.

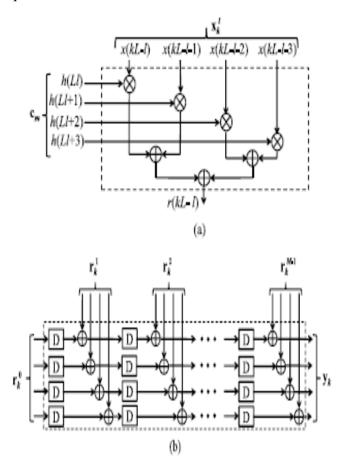

Each IPU performs lattice vector result of S0k with the short-weight vector cm and figures a square of L incomplete channel yields (rm k). In this manner, each IPU performs L inward item calculations of L lines of S0k with a typical weight vector cm. The structure of the (m+1) th IPU is appeared in Fig. 3(a). It comprises of L number of L-point internal item cells (IPCs). The (l+1) th IPC gets the (l+1) th

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

column of S0k and the coefficient vector cm and registers an incomplete consequence of internal item r (kL -l), for  $0 \le l \le L - 1$ . Interior structure of (l + 1) th IPC for L = 4 is appeared in Fig. 3(a). All the M IPUs work in parallel and create M squares of result (rm k). These fractional inward items are included the PAU [shown in Fig. 3(b)] to get a square of L channel yields. In each cycle, the proposed structure gets a square of L information sources and creates a square of L channel yields, where the span of each cycle is  $T = TM + TA + TFA \log_2 L$ , TM is one multiplier delay, TA is one adder deferral, and TFA is one full-adder delay.

Fig. 2. Proposed structure for block FIR filter.

Fig. 3. (a) Internal structure of RU for block size L = 4. (b) Structure of (m + 1) th IPU.

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

### 3.1 MCM-Based Implementation of Fixed-Coefficient FIR Filter

The induction of MCM units for transpose shape squares FIR channel, and the plan of proposed structure for settled channels. For settled coefficient execution, the CSU of Fig. 4 is never again required, since the structure is to be customized for just a single given channel. So also, IPUs are not required. The augmentations are required to be mapped to the MCM units for a low-multifaceted nature acknowledgment. In the accompanying, we demonstrate that the proposed plan for MCM-based usage of square FIR channel makes utilization of the symmetry in information framework S0k to perform even and vertical regular sub expression disposal and to limit the quantity of move include activities in the MCM squares.

Fig. 4(a) Internal structure of (l + 1) th IPC for L = 4. (b) Structure of PAU for block size L = 4.

#### 4. Results and Discussion

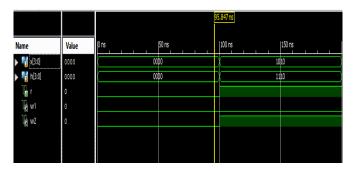

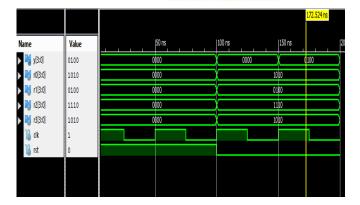

Fig. 5 Inner Product Cell results

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

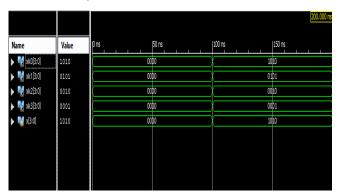

Fig. 6. Parallel adder unit results

Fig. 7. Register unit results

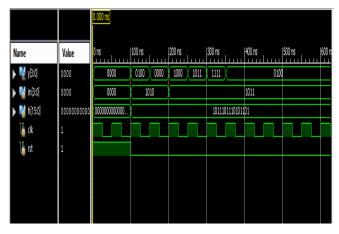

Fig. 8 Fir filter with Wallace tree multiplier results

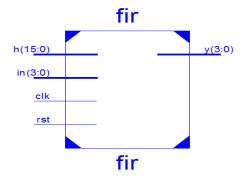

Fig. 9 RTL schematic

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

Fig. 10 Technology schematic

| Device Utilization Summary (estimated values) |      |        |        |             | Ð   |

|-----------------------------------------------|------|--------|--------|-------------|-----|

| Logic Utilization                             | Used | Availa | ble    | Utilization |     |

| Number of Slice Registers                     |      | 12     | 607200 |             | 0%  |

| Number of Slice LUTs                          |      | 18     | 303600 |             | 0%  |

| Number of fully used LUT-FF pairs             |      | 9      | 21     |             | 42% |

| Number of bonded IOBs                         |      | 18     | 700    |             | 2%  |

| Number of BUFG/BUFGCTRLs                      |      | 1      | 32     |             | 3%  |

Fig. 11 design summary

#### 5. Conclusion

In this paper, we have explored the possibility of realization of block FIR filters in transpose form configuration for area delay efficient realization of both fixed and reconfigurable applications. A generalized block formulation is presented for transpose form block FIR filter, and based on that we have derived transpose form block filter for reconfigurable applications. We have presented a scheme to identify the MCM blocks for horizontal and vertical subexpression elimination in the proposed block FIR filter for fixed coefficients to reduce the computational complexity. Performance comparison shows that the proposed structure involves significantly less ADP and less EPS than the existing block direct-form structure for medium or large filter lengths while for the short-length filters, the existing block direct-form structure has less ADP and less EPS than the proposed structure.

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

#### References

- [1] Yu Pan and Pramod Kumar Meher, Senior Member, IEEE, "Bit-Level Optimization of Adder-Trees for Multiple Constant Multiplications for Efficient FIR Filter Implementation," Transactions On Circuits And Systems—I: Regular Papers, Vol. 61, No. 2, February 2014.

- [2] D. R. Bull and D. H. Horrocks, "Crude administrator computerized channel," IEEE Proceedings-G, vol. 138, no. 3, pp. 401–412, Jun. 1991.

- [3] A. G. Dempster and M. D. Macleod, "Utilization of least snake multiplier hinders in FIR advanced channels," IEEE Trans. Circuits Syst. II, Analod Digit. Flag Process., vol. 42, no. 9, pp. 569–577, 1995.

- [4] S. D. S. M. Mehendale and G. Venkatesh, "Union of multiplier-less FIR channels with least number of increments," in Proc. IEEE ICCAD,1995.

- [5] I. C. Stop and H. J. Kang, "Computerized channel blend dependent on negligible marked digit portrayal," in Proc. Structure Autom. Conf. (DAC),2001.

- [6] Y. Voronenko and M. Püschel, "Multiplierless different steady augmentation," ACM Trans. Calculations, vol. 3, no. 2, 2007.

- [7] P. K. Meher and Y. Skillet, "Mcm-based usage of square fir channels for rapid and low-control applications," in Proc. VLSI and System-on-Chip (VLSI-SoC), 2011 IEEE/IFIP nineteenth Int. Conf., Oct.2011, pp. 118–121.

- [8] L. Aksoy, C. Lazzari, E. Costa, P. Flores, and J. Monteiro, "Structure of digit-sequential FIR channels: Algorithms, models, and a CAD apparatus," IEEE Trans. Large Scale Integration (VLSI) Syst., vol. 21, no. 3,pp. 498–511, Mar. 2013.

- [9] M. B. Gately, M. B. Yeary, and C. Y. Tang, "Different genuine steady duplication with enhanced cost model and voracious and ideal quests," in Proc. IEEE ISCAS, May 2012, pp. 588–591.

- [10] M. Kumm, P. Zipf, M. Faust, and C.- H. Chang, "Pipelined snake diagram advancement for rapid various steady increase," in Proc.IEEE ISCAS, May 2012, pp. 49–52.

- [11] R. Hartley and A. Casavant, "Tree-stature minimization in pipelined models," in Proc. IEEE ICCAD, Nov. 1989.