A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

# DESIGN OF A LOW POWER SERIAL- PARALLEL MULTIPLIER WITH USING MODIFIED RADIX 4 BOOTH ENCODING

JUTUR PUSHPA RANI<sup>1</sup>, T.RAJESWARI<sup>2</sup>

<sup>1</sup>PG Scholar, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India <sup>2</sup> Assistant Professor, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India

**ABSTRACT:** In this paper, we present a two-speed, radix-4, sequential equal multiplier for speeding up applications like advanced channels, counterfeit neural organizations, and other AI calculations. Our multiplier is a variation of the sequential equal (SP) altered radix-4 Booth multiplier that adds just the nonzero Booth encodings and skirts the zero tasks, making the idleness subject to the multiplier esteem. Two subcircuits with various basic ways are used so throughput and inertness are improved for a subset of multiplier esteems. The multiplier is assessed on an Intel Cyclone V field-programmable door cluster against standard equal and SP multipliers across four diverse interaction voltage—temperature corners.

#### 1. INTRODUCTION

Multiplication is seemingly the main crude for advanced sign preparing (DSP) and AI (ML) applications, directing the region, deferral, and generally execution of equal executions. The work on the advancement of increase circuits has been broad, be that as it may, the adjusted Booth calculation at higher radixes in mix with Wallace or Dadda tree has commonly been acknowledged as the most noteworthy performing general issues. execution for computerized circuits, increase is for the most part acted in one of three different ways: 1) equal; 2) sequential equal (SP); and 3) sequential. Utilizing the altered Booth calculation [5], [6], we investigate a SP two-speed multiplier (TSM) that restrictively adds the nonzero encoded portions of the augmentation and skirts the zero encoded areas.

In DSP and ML executions, decreased accuracy portrayals are frequently used to work on the presentation of a plan,

making progress toward the littlest conceivable bit width to accomplish an computational exactness ideal Accuracy is typically fixed configuration time, and consequently, any progressions in the prerequisites require that further adjustment includes update of the execution. In situations where a more modest bit width would be adequate, the plan runs at a lower productivity since superfluous calculation is attempted. To alleviate this, blended accuracy calculations endeavor to utilize a lower bit width some part of time, and a huge bit width when important [8]–[10]. These are typically carried out with two datapaths working at various precisions. This paper acquaints a powerful control structure with eliminate portions of the calculation totally during runtime. This is finished utilizing a changed sequential Booth multiplier, which skirts encoded each of the zero or every one of the one calculations, free of area. The multiplier

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

takes all pieces of the two operands in equal and is intended to be a crude square which is effectively consolidated into existing DSPs, CPUs, and GPUs. For certain info sets, the multiplier accomplishes impressive enhancements in computational execution. A critical component of the multiplier is that sparsity inside the information set and the inner twofold portrayal both lead to execution upgrades. The multiplier was tried utilizing field-programmable door exhibit (FPGA) innovation, representing interaction four diverse voltagetemperature (PVT) corners. principle commitments of this paper are as per the following.

- 1) The main sequential adjusted Booth multiplier where the datapath is separated into two subcircuits, each working with an alternate basic way.

- 2) Demonstrations of how this multiplier exploits specific bit-examples to perform less work; this outcomes in decreased idleness, expanded throughput, and prevalent region time execution than customary multipliers.

- 3) A model for assessing the exhibition of the multiplier and assessment of the utility of the proposed multiplier through a FPGA execution.

However, the fact remains that the area conflicting and speed are two performance constraints. Hence, innovating increased speed always results in larger area. The proposed architecture enhances the speed performance of the widely acknowledged Wallace tree multiplier when implemented on a FPGA. The structural optimization is performed on the conventional Wallace multiplier, in such a way that the latency of the total

circuit reduces considerably. A truncated multiplier with constant correction has the maximum error if the partial products in the n-k least significant columns are all ones or all zeros. A variable correction truncated multiplier has been proposed. This method changes the correction term based on column nk-1. If all partial products in column n-k-1 are one, then the correction term is increased. Similarly, if all partial products in this column are zero, the correction term is decreased. In a multiplier block is simplified 22 proposed for building larger multiplier arrays. In the design of a fast multiplier, compressors have been widely used to speed up the partial product reduction tree and decrease power dissipation. Kelly et al. and Ma et al. have also considered compression for approximate multiplication. An approximate signed multiplier has been proposed for use in arithmetic data value speculation (AVDS); multiplication is performed using the Baugh Wooley algorithm. However no new design is proposed for the compressors for the inexact computation.

#### 2.LITERATURE SURVEY

A signed binary multiplication technique by A. D. Booth

The advances of computerized math procedures grant PC originators to execute rapid application explicit chips. The presently delivered computerized circuits have shown superior as far as a few rules, for example, high clock rate, short information/yield delay, little region, low force silicon and dissemination. In this paper, we carry out a few sinusoidal age strategies to upgrade their exhibition and yield

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

utilizing progressed advanced numbercrunching procedures. In this paper, the executions of cutting edge advanced oscillator structures with and without pipelining proposed. The are combination consequences of the pipelining execution with have demonstrated that it is better than other sinusoidal age techniques as far as the most extreme recurrence and sign goal. Thus, this strategy is utilized in the plan of the proposed computerized oscillator chip.

Comparison of regular and tree based multiplier architectures with modified booth encoding for 4 bits on layout level using 45 nm technology by B. Dinesh, V. Venkateshwaran, P. Kavinmalar, and M. Kathirvelu

Multipliers are key parts of numerous superior frameworks, for example, FIR channels, chip, computerized signal processors, and so forth A framework's presentation is by and large controlled by the exhibition of the multiplier as the multiplier is for the most part the slowest component in the framework. investigation of execution boundaries of multiplier various rationales fundamental for plan of a framework expected for a particular capacity with limitations on Power, Area and Delay. The paper presents a point by point investigation of the multitude of sequential equal and equal structures. The multipliers are intended for 4 bit augmentation utilizing DSCH device and the comparing formats are gotten Microwind utilizing 3.5 apparatus utilizing 45nm innovation. From the examination it is seen that the exhibit multipliers give an ordinary directing design which will be ideal for FPGA

based frameworks. Among the tree based multipliers Dadda multipliers enjoy a slight upper hand over Wallace tree multipliers as far as execution. The Modified stall multiplier is relatively wasteful for bits lesser than or equivalent to 4, because of the expanded region required for acknowledgment of the corner encoder and stall selector blocks. The examination shows that for lower request bits Dadda decrease is the most productive.

A proof of the modified Booth's algorithm for multiplication by L. P. Rubinfield

An improved on evidence of an adjustment of Booth's increase calculation by MacSorley to a structure which inspects three multiplier bits all at once is introduced. In correlation with the first Booth's calculation, which inspects two pieces all at once, the adjusted calculation requires a large portion of the nutmber of cycles at the expense of to some degree expanded intricacy for every emphasis.

#### 3.PROPOSED SYSTEM

Radix-4 Booth algorithm is the parallel–serial multiplier. This computes  $x \times y$  where x and y are the n bit two's complement numbers (the multiplicand and multiplier respectively); producing a 2n two's complement value in the product p. The multiplication algorithm considers multiple digits of Y at a time and is computed in N partitions where

$$N = \left| \frac{n+2}{2} \right|.$$

-

An equation describing the computation is given by

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

$$p = (Y_1 + Y_0)x + \sum_{i=1}^{N} 2^{2i-1} (Y_{2i+1} + Y_{2i} - 2Y_{2i-1})x.$$

Y indicates the length-N digit vector of the multiplier y. The radix-4 Booth calculation considers three digits of the multiplier Y at a time to create an encoding e given by

$$e_i = Y_{2i+1} + Y_{2i} - 2Y_{2i-1}$$

3

| $Y_{i+2}$ | $Y_{i+1}$ | $Y_i$ | $e_i$                       |

|-----------|-----------|-------|-----------------------------|

| 0         | 0         | 0     | 0                           |

| 0         | 0         | 1     | 1                           |

| 0         | 1         | 0     | 1                           |

| 0         | 1         | 1     | 2                           |

| 1         | 0         | 0     | $\frac{2}{2}$ $\frac{1}{1}$ |

| 1         | 0         | 1     | $\overline{1}$              |

| 1         | 1         | 0     | $\overline{1}$              |

| 1         | 1         | 1     | 0                           |

TABLE I BOOTH ENCODING

where I indicates the I th digit. As outlined in Table I, separated from Yi+2Yi+1Yi = 000 and Yi+2Yi+1Yi = 111 which results in a 0, the multiplicand is scaled by one or the other 1, 2, -2, or -1 contingent upon the encoding.

This encoding ei is utilized to work out an incomplete item Partial Product i by working out

$$Partial Product_i = e_i x = (Y_{2i+1} + Y_{2i} - 2Y_{2i-1})x.$$

This Partial Product is adjusted utilizing a left shift (22i-1) and the summation is performed to compute the end-product p. Since the Y-1 digit is nonexistent, the 0th halfway item PartialProduct0 = (Y1+Y0)x. A sequential (consecutive) rendition of the augmentation is performed by figuring every incomplete item in N cycles

$$p[0] = 2^{n-2}(Y_1 + Y_0)x$$

$$p[j+1] = 2^{-2}(p[j] + 2^n(Y_{2j+1} + Y_{2j} - 2Y_{2j-1})x),$$

$$j = 1, ..., N-1$$

Two improvements are performed to take into account better equipment usage. In the first place, the item p is doled out the multiplier y (p = y), this eliminates the need to store y in a different register and uses the n LSBs of the p register. Subsequently, as the item p is moved right (p = sra(p, 2)), the following encoding ei can be determined from the three LSBs of p. The subsequent improvement eliminates the realignment left shift of the fractional item (2n) by aggregating the Partial Product to the n generally huge pieces of the item p (P[2 B-1 : B]+ = Partial Product).

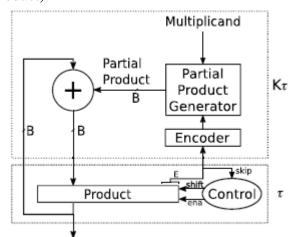

Fig. 1. n bit TSM. This contains an added control circuit for skipping and operating with two different delay paths

The sequential Booth duplication calculation and execution. The key change is to parcel the circuit into two ways; each having basic ways, T and KT, separately (see Fig. 3). The multiplier is timed at a recurrence of

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

(1/T), where the KT district is a completely combinatorial circuit with a deferral of KT. K is the proportion of the postponements between the two subcircuits. K = # is the quantity of cycles required for the expansion to be finished prior to putting away the outcome in the item register; utilized in the equipment execution of the multiplier.

As delineated in Algorithm 2, preceding playing out the expansion, the encoding, e (the three LSBs of the item) is inspected and a choice is made between two cases: 1) the encoding and PartialProduct are zero and 0x, individually, and 2) the encoding is nonzero. These two cases can be recognized by creating

$$skip = \begin{cases} 1, & \text{if } P[2:0] \in \{000, 111\} \\ 0, & \text{otherwise.} \end{cases}$$

6

At the point when skip = 1 just the right shift and cycle counter collect should be performed, with a basic way of T. On account of a nonzero encoding (skip = 0), the circuit is timed .K occasions at T. This guarantees adequate engendering time inside the viper and fractional item generator, permitting the item register to planning limitations. respect its Consequently, the aggregate time T taken by the multiplier can communicated as (11), where N is characterized by (5), and O is the quantity of nonzero encodings in the multiplier's Y digit vector The time taken to play out the increase is reliant on the encoding of the pieces inside the multiplier y. The upper also, lower headed for the absolute execution time happens when O = N and O = 0, individually. From (11), the maximum

and min Are The information that outcomes in the base execution time is at the point when y = 0. For this situation, all pieces inside the multiplier are 0, furthermore, every three LSB encoding brings about a 0x scaling and O = 0. There are a couple of info mixes that outcome in the most pessimistic scenario, O = N. One case would be various exchanging 0 and 1, i.e., 1010101..10101..10101..10101. For this situation, each encoding results in a nonzero Partial Product.

#### A. Control

As displayed in Fig. 4(a) and (b), the control circuit comprises predominantly of: one log2(N) collector, one log2(.K) gatherer, three doors to recognize the nonzero encodings, and a comparator. Counter2 is liable for checking the number of cycles required for the expansion without abusing any planning limitations, i.e., .K . At the point when the encoding is nonzero, Counter2 is augmented. Counter1 aggregates the number of encodings that have been prepared. As the quantity of cycles expected to finish a solitary duplication is N, hence, the collector and Counter1 should be log2(N) bits wide. Counter1 is augmented when comparator the condition has been met, Counter2 = .K, or a zero encoding is experienced. At the point when Counter1 increases, the sign is given to play out the right shift. The control needs to recognize the zero and nonzero encodings. It contains a threedoor circuit, performing (10); taking in the three LSBs of the multiplier v. Two instances of zero encoding exist. The three doors are intended to recognize these nonzero encodings; an inverter is

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

associated with the collector of Counter2, augmenting, in these cases.

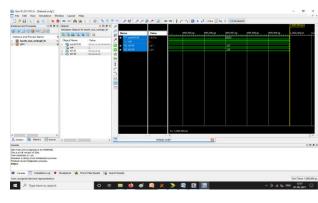

### **4.SIMULATION RESULT OF MULTIPLIER:**

Fig 2 Simulation Result of Multiplier

Here we can give the inputs as A=126, B=127, then the final output is 16002.

#### **5 CONCLUSION**

We presented a TSM, which is divided into two subcircuits, each operating with a different critical path. In real time, the performance of this multiplier can be improved solely on the distribution of the bit representation. We illustrated for bit widths of 8 and 16, typical compute sets, such as uniform and Gaussian and neural networks, can expect substantial improvements of 3x and 3.56x using standard learning and sparse techniques, respectively. The cost associated with handling lower bit width representations, such as Gaussian-8 on a 8-bit multiplier is alleviated and show up to a 3.64× improvement compared to the typical parallel multiplier. Future work will focus on techniques for constructing applications to take full advantage of the two-speed optimization

#### **6 FUTURE SCOPE**

This multipliers plays a very important role in our day to day life. In future the multipliers are going to play a major role. The speed of the multipliers are increased by using carry save adders, carry look ahead adder, and so on. Rounding patterns will be optimized based on required accuracy and different compression techniques. The area and delay can be reduced in future by using advanced technology.

#### **BIBLIOGRAPHY**

- [1] A. D. Booth, "A signed binary multiplication technique," Quart. J. Mech. Appl. Math., vol. 4, no. 2, pp. 236–240, 1951.

- [2] B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs. New York, NY, USA: Oxford Univ. Press, 2000.

- [3] M. D. Ercegovac and T. Lang, Digital Arithmetic (Morgan Kaufmann Series in Computer Architecture and Design). San Mateo, CA, USA: Morgan Kaufmann, 2004.

- [4] B. Dinesh, V. Venkateshwaran, P. Kavinmalar, and M. Kathirvelu, "Comparison of regular and tree based multiplier architectures with modified booth encoding for 4 bits on layout level using 45 nm technology," in Proc. Int. Conf. Green Comput. Commun. Elect. Eng., Mar. 2014, pp. 1–6.

- [5] O. L. MacSorley, "High-speed arithmetic in binary computers," Proc. IRE, vol. PROC-49, no. 1, pp. 67–91, Jan. 1961.

- [6] L. P. Rubinfield, "A proof of the modified Booth's algorithm for multiplication," IEEE Trans. Comput.,

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

vol. C-24, no. 10, pp. 1014–1015, Oct. 1975, doi: 10.1109/T-C.1975.224114.

[7] P. Judd, J. Albericio, T. Hetherington, T. M. Aamodt, and A. Moshovos, "Stripes: Bit-serial deep neural network computing," in Proc. 49th Annu. IEEE/ACM Int. Symp. Microarchitecture, Oct. 2016, pp. 1–12.

[8] G. C. T. Chow, W. Luk, and P. H. W. Leong, "A mixed precision methodology for mathematical optimisation," in Proc. IEEE 20<sup>th</sup> Int. Symp. Field-Program. Custom Comput. Mach., Apr./May 2012, pp. 33–36.

[9] G. C. T. Chow, A. H. T. Tse, Q. Jin, W. Luk, P. H. Leong, and D. B. Thomas, "A mixed precision Monte Carlo methodology for reconfigurable accelerator systems," in Proc. ACM/SIGDA Int. Symp. Field Program. Gate Arrays, 2012, pp. 57–66.

[10] S. J. Schmidt and D. Boland, "Dynamic bitwidth assignment for efficient dot products," in Proc. Int. Conf. Field Program. Log. Appl., Sep. 2017, pp. 1–8.

[11] V. Sze, Y.-H. Chen, J. Emer, A. Suleiman, and Z. Zhang, "Hardware for machine learning: Challenges and opportunities," CoRR, vol. abs/1612.07625, Dec. 2016. [Online]. Available:

https://arxiv.org/abs/1612.07625

[12] B. Rashidi, S. M. Sayedi, and R. R. Farashahi, "Design of a low-power and low-cost Booth-shift/add multiplexer-based multiplier," in Proc. Iranian Conf. Elect. Eng. (ICEE), May 2014, pp. 14–19

[13] P. Devi, G. P. Singh, and B. Singh, "Low power optimized array multiplier with reduced area," in High Performance Architecture and Grid Computing, A.

Mantri, S. Nandi, G. Kumar, and S. Kumar, Eds. Berlin, Germany: Springer, 2011, pp. 224–232.