A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

# DESIGN AND IMPLEMENTATION OF HIGH SPEED FT\_FFT 1V.SNEHA, 2Y.BHASKARA RAO

<sup>1</sup>B.Tech Scholar, Dept of ECE, Malineni Lakshmaiah Women's Engineering College, Guntur, Andhra Pradesh

<sup>2</sup>Associate Professor, Dept of ECE, Malineni Lakshmaiah Women's Engineering College, Guntur, Andhra

Pradesh

**ABSTRACT:** In this paper design and implementation of high speed FT\_FFT is going to be done. Basically the FFT supports the bit size which is suitable to the system and mostly used in the long term evolution systems. Transport triggered architecture is utilized to customize the size of fault free FFT processor. Here the both energy-efficiency and performance is evaluated by using the standard cell technology. FFT flag register is used to store the input data. Program control unit is used to control the entire system while processing its operation. The processed data in program control unit will save it in program memory. FFT Address generation unit generates the address to access the main memory. Data processing unit will process the data. FT\_FFT block will perform the operation and gives output and saved in the output register and reduce the errors by using fault tolerant technique. From results it can observe that the proposed system gives effective output.

# **KEY WORDS: FFT, Computation, Adder, Multiplier, Computing Address, Generator Memory Bank.**

#### **I.INTRODUCTION**

Generally, discrete Fourier transform is introduced in 1965. Basically, the discrete Fourier transform is taken from the fast Fourier calculation. All things considered, after practically 50 years, stays extremely high because of key helpful properties of DFT. The ongoing increase in such intrigue is because of correspondence applications, specifically Long Term Evolution (LTE) and Software Defined Radio (SDR) [1]. In these applications, productive usage of DFT are required so as to help very tight, commonly negating limitations, for example, hard ongoing necessities over low-control,

Minimal effort and adaptable HW stages. In the OFDM images using the Discrete Fourier to obtain the high speed operation in the system. Here the length of each image is considered as N and these produces complex quantities in the entire system. Hence the vector image is used with the length of N = 128. In the Meantime, the plan eases to be valuable and the primary target gadgets are compact purchaser Electronics, for example, portable (advanced cells,) workstations, and so forth. Then again, plans of action require adaptable programmable usage [2].

Basically, the main intent of filters is to use partial range of frequency to emphasize the signals. But here the signals are getting rejected because of selection of frequency range in alternate way. Coming to the designing part of circuit, the frequency is selected alternatively. Here the frequency range is connected to the electric network. This electric network works depending on characteristics signals. the of The characteristic parameters are amplitude, frequency and time [3].

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

Depending on these parameters the entire electric network works. Here this may come to know that, there will be no change in allotted frequency and as well as cannot add new frequency to the system. Filters are mainly used in the applications of medical, automotive. There is a unity of region with some very surprising bases characterization channels and these cover in some unique ways; there is no direct hierarchical grouping. As the social properties of the sign change, separation strategies will be considered.

FFT is an elective calculation procedure for discrete Fourier change as it registers rapidly. FFTs are utilized in countless applications extending from advanced sign furthermore preparing and calculations, for example, understanding the incomplete differential conditions. augmentation of enormous esteem whole numbers and so forth. FFT processor working recurrence decides the range for which the processor can be utilized. The processor is intended to figure countless complex increases both at rapid and with reliable throughput.

The other design challenges are found in the way in which, by changing the number of centers in FFT, the processor can be suitable for several applications that work both from the structure and from sensitive applications. Despite the way in which this is apparently useful, the fluctuation of the number of centers emphasizes different changes both at the registration level and through the change in the number of bits and the level of construction based on the variation in the length of the displacement registers, analogously to regulation of the meaning of ROM.

#### **II.FFT PROCESSOR**

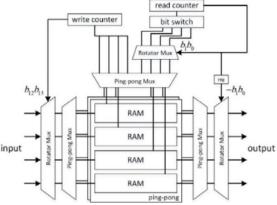

The below figure (1) shows the architecture of FFT processor system. In the memory based FFT processor architecture is using two modules and this can performs fast opeartions without zero padding. Here radix architecture is shown and multipliers are used. All these components combine together and gives the specified output.

In this memory based FFT processor system, for the purpose of modular reduction and conditional sequences are using the number of muliple opeartions units. Here the pipeline architectures are designed inside the each unit and the entire operation is performed sequentially. Next coming to the block butterfly unit, it performs the forward and inverse operation. In multiple adder unit, the component wise multiplication and addition operations are performed. Now for the time domian operations are using the ripple carry adder, subractor and module units. Control unit is used to generate the control signals in the system. Coming to memory, it consists of several RAM sets which stores the precomputed data and intermidiate results.

Fig. 1: FFT PROCESSOR

The first and principle significant part in the design is multiply and adder unit. This unit

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

actualizes the segment insightful augmentation and expansion of FFT-RAM. To understand the segment savvy increase when operand size isn't bigger than couple of hundred bits then karatsuba technique is utilized. The multiplier and adder units works with pipeline of 3 bit data sources and one piece yield. Finally to improve the presentation of increase, karatsuba strategy is connected recursively. This is about duplicate and snake unit and let us examine about FFT unit.

Next it is connected to FFT calculation. The principle correlation of set up and consistent geometry FFT is it has same association arrange between each neighboring stages. The FFT is structured with six data sources. In this the four contributions forward the digits into BFSs for FFT calculation and the other two contributions forward the preregistered upper bound imperatives into FSO.

#### III. RECONFIGURABLE MEMORY BASED FFT

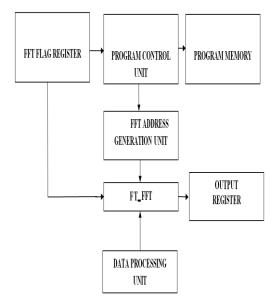

The below figure (2) shows the block diagram of proposed system. FFT flag register is used to store the input data. Program control unit is used to control the entire system while processing its operation. The processed data in program control unit will save it in program memory. FT\_FFT Address generation unit generates the address to access the main memory. Data processing unit will process the data. FFT block will perform the operation and gives output and saved in the output register.

Fig. 2: PROPOSED SYSTEM

A Fast Fourier Transform (FFT) is an estimate that represents the Discrete Fourier Transform (DFT) of a meeting or its round (IDFT). Fourier's examination changes on a of this extraordinary sign region (occasionally time or space) representation in the space of repetition and in a different way. DFT is obtained by breaking down a progression characteristics different in frequency portions. This action is important in several fields, but its direct management from the definition is as frequent as possible, moderate excessively possibly or conventional.

PCU is an execution unit inside Control Processing Units (CPUs) that ascertains addresses utilized by the CPU to get to primary memory. By having address estimations taken care of by discrete hardware that works in parallel with the remainder of the CPU, the quantity of CPU cycles required for executing different machine directions can be diminished, bringing execution upgrades. While

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

performing different tasks, CPUs need to compute memory tends to required for bringing information from the memory; for instance, in-memory places of exhibit components must be determined before the CPU can get the information from genuine memory areas. Those location age computations include distinctive number-crunching tasks, for example, expansion, subtraction, modulo activities, or bit shifts.

The technique that is utilized to exchange data between inward capacity and outer gadgets is known as I/O interface. The CPU is interfaced utilizing unique correspondence interfaces by the peripherals associated with any PC framework. These correspondence connections are utilized to determine the contrasts among CPU and fringe. There exists extraordinary equipment parts among CPU and peripherals to administer and synchronize all the info and yield exchanges that are called interface units.

FAGU are utilized in direct current (DC) machines: dynamos (DC generators) and numerous DC engines just as widespread engines. In an engine the commutator applies electric flow to the windings. By switching the present bearing in the pivoting windings every half turn, a consistent pivoting power (torque) is delivered. At least two electrical contacts called "brushes" made of a delicate conductive material like carbon press against the commutator, reaching progressive sections of the commutator as it pivots. The windings (loops of wire) on the armature are associated with the commutator portions.

#### IV. RESULTS

The below figure (3) shows the RTL schematic of proposed system.

Fig. 3: RTL SCHEMATIC

The below figure (4) shows the technology schematic of proposed system.

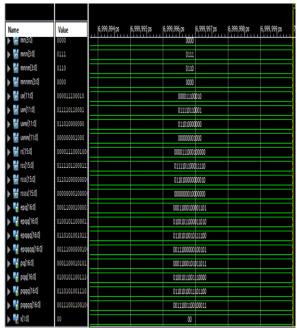

| Name                      | Value         | ш | 6,999,994 ps | 6,999,995 ps | 6,999,996 ps | 6,999,997 ps | 6,999,998 ps | 6,999,999 ps |

|---------------------------|---------------|---|--------------|--------------|--------------|--------------|--------------|--------------|

| ▶ 🛂 zz[15:0]              | 0010101100101 |   |              |              | 0010101100   | 01011        |              |              |

| <b>▶</b> 🛂 m[15:0]        | 0101101101010 |   |              |              | 0101101101   | 10110        |              |              |

| I mm [15:0]               | 0110110010101 |   |              |              | 0110110010   | 01010        |              |              |

| <b>&gt; 🛂 2222</b> [15:0] | 0101001010100 |   |              |              | 0101001010   | 00010        |              |              |

| ▶ 👫 a[70]                 | 00101100      |   |              |              | 001011       | 0            |              |              |

| <b>▶ 🕌</b> aa[7:0]        | 01010101      |   |              |              | 010101       | 1            |              |              |

| <b>▶ 🕌</b> aaa 7:0        | 10011101      |   |              |              | 1001111      | 1            |              |              |

| <b>▶ 🕌</b> aaaa[7:0]      | 10011101      |   |              |              | 1001111      | 1            |              |              |

| <b>▶ 🕌</b> b[7:0]         | 00100100      |   |              |              | 001001       | 0            |              |              |

| <b>▶</b> 🛂 bb[7:0]        | 10110010      |   |              |              | 101100       | 0            |              |              |

| <b>▶</b> 🖁 bbb[7:0]       | 10101010      |   |              |              | 1010101      | 0            |              |              |

| <b>&gt; №</b> bbbb[7:0]   | 00110101      |   |              |              | 001101       | 1            |              |              |

Fig. 4: INPUT WAVEFORM

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

Fig. 5: OUTPUT WAVEFORM

#### V. CONCLUSION

Hence in this design and implementation of high speed FT\_FFT was done. FFT flag register is used to store the input data. Program control unit is used to control the entire system while processing its operation. The processed data in program control unit will save it in program memory. FAGU FFT Address generation unit generates the address to access the main memory. Data processing unit will process the data. FFT block will perform the operation and gives output and saved in the output register. From results, it can observe that the proposed system gives effective output.

#### VI. REFERENCES

[1] Yu Xie, Chen Yang, Chuang-An Mao, He Chen and Yi□ Zhuang Xie, "A Novel Low-Overhead Fault Tolerant Parallel Pipelined FFT Design", 978-1-5386-0362-8/17/\$31.00 №2017 IEEE.

[2] Syed M. A. H. Jafri, Stanisław J. Piestrak, Kolin Paul, Ahmed Hemani, Juha

Plosila, and Hannu Tenhunen, "Energy-Aware Fault-Tolerant CGRAs Addressing Application with Different Reliability Needs", '/13 \$26.00 © 2013 IEEE.

[3] Abbas BanaiyanMofrad, Houman Homayoun, Nikil Dutt, "FFT-Cache: A Flexible Fault-Tolerant Cache Architecture for Ultra Low Voltage Operation", CASES'11, October 9–14, 2011, Taipei, Taiwan.

[4] C. Radhakrishnan and W. K. Jenkinss, "Fault Tolerant Adaptive Filters Based on Modified Discrete Fourier Transform Architectures", 978-1-4244-9474-3/11/\$26.00 ©2011 IEEE.

[5] Hongyi Fu, Xuejun Yang, "Fault Tolerant Parallel FFT Using Parallel Failure recovery", 978-0-7695-3701-6/09 \$25.00 © 2009 IEEE.

[6] Jin-Fu Li, Shyue-Kung Lu, Shih-Arn Hwang, "Easily Testable and Fault-Tolerant FFT Butterfly Networks", 1057–7130/00\$10.00 © 2000 IEEE.

[7] G. Robert Redinbo, Ranjit Manomohan, "Fault-Tolerant FFT Data Compression", 0-7695-0975-4100 \$10.00 0 2000 IEEE.

[8] Jin-Fu Li and Cheng-Wen Wu, "Testable and Fault Tolerant Design for FFT Networks", 1999 IEEE Conference.

[9] Shyue-Kung Lu, Cheng-Wen, Wu Sy-Yen Kuo, "On Fault-Tolerant Fft Butterfly Network Design", 0-7803-3073-0/96/\$5 .OO @ 1996 IEEE.

[10] Bernard A. Schnaufer and W. Kenneth Jenkins, "A Fault Tolerant FIR Adaptive Filter Based on the FFT", 0-7803-1775-On4 \$3.00 0 1994 IEEE.