> A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

## HIGH-SPEED SCALABLE MODELING OF MEMORY CELL BASED ON NMOS DIGITAL LDO <sup>1</sup>KOMMU PAVAN KUMAR, <sup>2</sup>SRIVENKATA SESHU ARAVIND R <sup>1</sup>M.Tech scholar, Dept of ECE, Eluru College of Engineering & Technology, Duggirala Village, Eluru, Andhra Pradesh, India

<sup>2</sup>Assistant Professor, Dept of ECE, Eluru College of Engineering & Technology, Duggirala Village, Eluru, Andhra Pradesh, India

### **ABSTRACT:**

In this paper high speed scalable modeling of memory cell based on NMOS digital LDO is implemented. Basically, the main intent of digitally controlled Low Dropout regulator (LDO) is to perform the fast transient and auto tuned voltage. LDO is mainly used in the applications of system on chips and memory. Earlier, conventional LDO is implemented, but there will be more usage of memory, MOSFET's and nodes. To overcome this memory cell based on NMOS digital LDO is implemented. From results, it can observe that NMOS Digital LDO Based memory cell gives effective results in terms of MOSFET's, Nodes and memory usage.

KEY WORDS: LDO regulator, CMOS technology, small area, High stability.

### **I.INTRODUCTION**

The use of the battery control gadgets in the present worldwide town has turned out to be unavoidable and irreplaceable in pretty much varying social statuses. By decreasing the quantity of battery cells, cost and size of configuration get diminished. This may limit tranquil current stream and thus battery life increments. An expanding number of low voltage applications require the utilization of LDOs, which incorporate the developing group of versatile battery items. Voltage controllers give a steady voltage supply rail under all stacking conditions.

Most handheld, battery-fueled gadgets hardware high light power sparing methods to lessen control utilization. Low dropout and low supply current qualities of CMOS straight controllers discovered increasingly profitable in the realm of hardware [1]. LDO controllers empower battery to be spent to as far as possible, and along these lines the controllers are presently provide the basic power on the board of ICs for the gadgets like cell phones, computerized cameras, and workstation PCs to have long battery life. There has been an expanding request to plan a stable LDO for a wide scope of error conditions with high PSR(power supply rejection),low drop-out voltage and low quiet current [2].

In any case, it is observed to be hard to improve every one of them all the while. With the appearance of low power batteryworked circuits, requesting uncommon accentuation is on minimization and movability. The utilization of small transistor size empowers quicker transient reaction since slew-rate limit at the gate of the power transistor is moderately not genuine. So it has turned out to be basic to improve existing low drop-out controller structures for more noteworthy all-round execution. The path metric unit (PMU) idea moves scientists to concentrate on least supply voltage, quicker unique reaction, higher strength, small zone and less power utilization.

Volume 11, Issue 12, DEC 2021

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

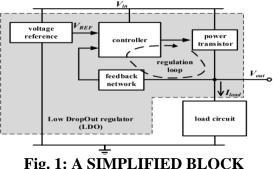

Fig. 1: A SIMPLIFIED BLOCK DIAGRAM OF AN LDO

Low dropout controllers have picked up significance because of interest for power effective circuits in portable correspondence applications, which require expanded battery life. The investigation of intensity the executives systems has expanded terrifically inside the most recent couple of years relating to a huge increment in the utilization of compact, handheld battery worked gadgets. A power board framework contains a few subsystems including straight controllers, exchanging controllers, and control logic. The control logic changes the characteristics of every subsystem, dividing the yields on and just as changing the yield voltage levels, to advance the power utilization of the gadget.

Recently acquainted designs furnish various procedures with segregate info and yield along the high current sign way. It is seen that nm innovation demonstrates better in accomplishing required execution particulars. We can utilize advanced control to satisfy requests for multifunction among shopper hardware, practical circuits which are incorporated as framework on chip (Soc). The outside control sign open or short the change transistors to change the criticism resistor divider proportion to accomplish a programmable yield voltage required by various applications. A fundamental LDO controller is made out of three primary parts biasing circuit, a mistake intensifier, a power MOS gadget [3].

The structure of the yield phase of the blunder speaker has sway on the required size of intensity transistor that improves load guideline particularly when the supply voltage is low. This paper displays a LDO controller utilizing a basic OTA-type mistake enhancer and versatile transient quickening agent which can accomplish activity underneath 1V with quick transient reaction, high PSR under a wide scope of working conditions. Primary center is to structure a programmable low-dropout (LDO) voltage controller that can work with a small info yield differential voltage with 32nm CMOS innovation whose yield voltage level is controlled remotely by methods for control signals [4].

Proposed configuration is a finished SOC (framework on chip) plan which gives many circuit applications in versatile, mechanical and medicinal areas. As future nm innovation offers more points of interest in accomplishing the majority of the exhibition determinations so it is gainful to propose the controller with the choice of lower request of nm innovation to satisfy focused on requests [5].

#### II. NMOS DIGITAL LDO WITH NAND-BASED ANALOG-ASSISTED LOOP

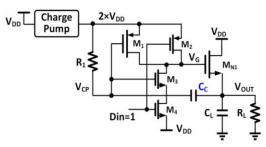

This work presents a NMOS computerized LDO with a NAND based simple helped way, which partakes in the low voltage high DC acquire advanced control (being the I way) and the quick transient reactions of the assistant simple PD ways, framing an effective PID control. Figure (2) shows the design of the proposed NMOS DLDO with NAP. Since the NMOS power semiconductor must be driven by a voltage

Volume 11, Issue 12, DEC 2021

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

that is one VGS higher than VOUT, a little charge siphon is utilized to control up the entryway drive stage, as displayed in Fig. 3.1. It is a double branch voltage doublers with a voltage transformation proportion of 2. The momentum required by the door drivers and the level shifters is tiny, and the flying capacitors and the separating capacitor are intended to be just 6pF each.

### Fig. 2: SCHEMATIC OF THE NAND-GATE-BASED HIGH-PASS ANALOG PATH

The advanced control circle. In light burden condition, the MSB of the DLDO power switches ought to be off, and the advanced control input Din is 1. Thusly, M2 is off, and M4 is on. The capacitor CC couples the yield transient sign to the VCP hub which is DC one-sided to 2×VDD by the resistor R1, so M1 is off and M3 is on. Then, at that point, VG is low, and the NMOS power switch MN1 is off. Here, VCP is associated with the contribution of a modified NAND entryway where the PMOS M1 has enormous W/L to intensify the coupled transient waveform.

The coupling capacitor CC is associated with M1, which frames an altering intensifying than stage, rather straightforwardly interfacing with the NMOS power switch that has a huge door capacitance. As the door capacitance of M1 is impressively more modest, the planned Cc is just 12pF. The green line is the transient response of the check DLDO using PMOS power switches, and VOUT has an undershoot voltage of 426 mV. The blue line is the transient response of the DLDO using NMOS power switches without the NAND based basic aided circle. The undershoot voltage is 244 mV, which is benefitted from the NMOS normal response. The red line is the transient response of the NMOS DLDO notwithstanding NAP, and the undershoot voltage is only 96 mV, which shows predominant transient response execution.

In the control circle, the comparator changes over the simple yield voltage signal into the computerized space. Three twofold tail comparators are utilized. The twofold tail comparator has three heaps of MOS semiconductors, which could work under lower supply voltage when contrasted with the conventional four-stack comparator. The comparators are set off by the information clock sign to test the yield voltage straightforwardly.

Because of coordinated activity, the control circuit gets the examination result just from the last rising edge of the clock, and the greatest excess season of one clock cycle the transient exhibition. corrupts То abbreviate the repetitive time, nonconcurrent rationale is utilized. Offbeat rationale flips the shift enlists in a split second when the comparator has identified the voltage change, by utilizing the comparator's status discovery rationale to trigger the fell rationale. The status location rationale recognizes if the comparator has completed the correlation and creates a "Substantial" signal, which is utilized to trigger the fell computerized hinders as opposed to utilizing the worldwide clock. When the comparator is reset, both Out-and Out + are 1. After completing examination, one of the yields changes to 0, and a NAND entryway is

utilized to produce the "Legitimate" signal.

#### III. MEMORY CELL BASED ON NMOS DIGITAL LDO

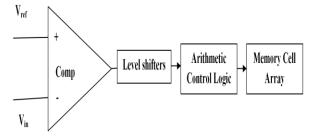

A low dropout or LDO controller is a DC straight voltage controller which has a particularly information minor vield differential voltage. The guideline modules are a power FET and a differential intensifier (bumble speaker). One information of the differential intensifier demonstrates a rate of the yield, as firm by the resistor extent of R1 and R2. The second information to the differential enhancer is from a consistent voltage reference (band opening reference). The below figure (3) shows the block diagram of memory cell based NMOS digital LDO. In this first input is given and after that the input data is shifted by using shifters. ALU will increase the speed of operation. Memory cell array will save the data.

### Fig. 3: BLOCK DIAGRAM OF MEMORY CELL BASED NMOS DIGITAL LDO

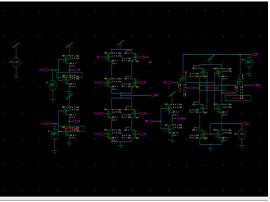

The below figure (4) shows the schematic of block diagram of memory cell based NMOS digital LDO. In this 22 MOSFET's are utilized to design. The total delay is obtained while designing this schematic is 3.39 ns.

Fig. 4: SCHEMATIC OF MEMORY CELL BASED NMOS DIGITAL LDO

In the off-chip capacitor less LDO voltage controller, the generally small and errors subject to chip yield capacitor can't be utilized to make the predominant post since the yield shaft must live at high recurrence. Along these lines, the prevailing shaft must be set inside the blunder intensifier control circle, and transient control sign must proliferate through an interior predominant post previously or at the door of the pass transistor. The pass transistor involves the most significant component supplies current to the heap impedance and therefore builds up the ideal yield voltage.

Transistor gate capacitance and yield obstruction of mistake enhancer goes about as a current to voltage converter, and consequently, has an identical spread postponement. The bigger the gate capacitance is, the bigger the proliferation defer will be. On account of the pass transistor, the successful info door capacitance incredibly is enormous. Accordingly, a circuit is required that improves the speed of charging the door of the pass transistor.

An assistant quick circle (differentiator), as appeared in schematic repays LDO controller. The differentiator shapes the

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

foundation of the design giving both a quick transient locator way just as inner air conditioning remuneration. The least complex coupling system may be a solidarity increase current support detects the adjustments in the yield voltage as a current. The current is then infused into pass transistor gate capacitance by methods for the coupling system.

## V. RESULTS

The below figure (5) shows the synthesis report of memory cell based NMOS digital LDO. This synthesis report is the combination of MOSFET's, total Nodes, Independent nodes, Boundary nodes, parsing delay and set up delay.

| Device and node counts: |              |

|-------------------------|--------------|

| MOSFETs -               | 22           |

| MOSFET geometries -     | 2            |

| Voltage sources -       | 5            |

| Subcircuits -           | 0            |

| Model Definitions -     | 6            |

| Computed Models -       | 2            |

| Independent nodes -     | 12           |

| Boundary nodes -        | 6            |

| Total nodes -           | 18           |

|                         |              |

| Parsing                 | 0.40 seconds |

| Setup                   | 0.76 seconds |

| DC operating point      | 0.95 seconds |

| Transient Analysis      | 0.01 seconds |

| Overhead                | 1.27 seconds |

|                         |              |

| Total                   | 3.39 seconds |

|                         |              |

| Simulation completed    |              |

### Fig. 5: SYNTHESIS REPORT

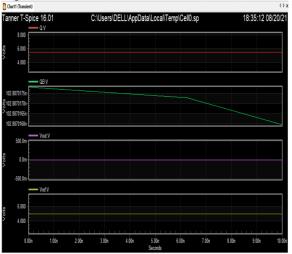

The below figure (6) shows the output waveform of memory cell based NMOS digital LDO.

Fig. 6: OUTPUT WAVEFORM

### VI. CONCLUSION

Hence in this paper high speed scalable modeling of memory cell based on NMOS digital LDO was implemented. LDO is mainly used in the applications of system on chips and memory. From results, it can observe that NMOS Digital LDO Based memory cell gives effective results in terms of MOSFET's, Nodes and memory usage.

In future we can extend this project by increasing the number of bits and it can also implemented in hardware kit. We can also extend this project using GDI technology.

#### VII. REFERENCES

[1] Xiaofei, Yan Lu, Qiang Li "An NMOS digital LDO with NAND based analog assisted loop in 28-nm CMOS," 1549-8328 © 2020 IEEE.

[2] Hung-Chih Lin, Hsiang-Han Wu, and Tsin-Yuan Chang, "An Active-Frequency Compensation Scheme for CMOS Low-Dropout Regulators with Transient-Response Improvement," IEEE Transactions on Circuits and Systems—II: Express Briefs, VOL. 55, NO. 9, September 2008.

[3] Socheat Heng and Cong-Kha Pham, "A Low-Power High-PSRR Low-Dropout Regulator with Bulk-Gate Controlled Circuit," IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 57, No. 4, April 2010.

[4] Liake Wang, Jinguang Jiang, Shanshan Li, Xu Gong and Qingy un Li, "A High Stability Low Drop-out Regulator With Fast Transient Response," IEEE 978- 1-4244-5849-3/10/\$26.00 ©2010.

[5] Robert J. Milliken, Jose Silva-Martínez, and Edgar Sánchez-Sinencio, " Full On-Chip CMOS LowDropout Voltage Regulator," IEEE Transactions on Circuits

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

and Systems—I: Regular Papers, Vol. 54, No. 9, September 2007.

[6] SreehariRao Patri, and K. S. R. KrishnaPrasad, "Self Compensating ON Chip LDO Voltage Regulator in 180nm," World Academy of Science, Engineering and Technology 44 2008.

[7] Peter Hazucha, Tanay Karnik, Bradley A. Bloechel, Colleen Parsons, David Finan, and Shekhar Borkar, "Area-Efficient Linear Regulator With Ultra-Fast Load Regulation," IEEE Journal of Solid-State Circuits, Vol. 40, No. 4, April 2005.

[8] David C. W. Ng, David K. K. Kwong, and Ngai Wong, "A Sub-1 V, 26 W, Low-Output-Impedance CMOS Bandgap Reference With a Low Dropout or Source Follower Mode," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 7, July 2011.

[9] Chenchang Zhan, and Wing-Hung Ki, "OutputCapacitor-Free Adaptively Biased Low-Dropout Regulator for System-on-Chips," IEEE Transactions on Circuits and Systems—I: Regular Papers, Vol. 57, No. 5, May 2010.

[10]Abdul Naim Khan and Sandeep Kumar Toshniwal, "Multi-level CMOS LDO-Voltage Circuit with Differential Current Circuit Steering and Regulated Voltage," IOSR Journal of VLSI and Signal Processing, Volume 5, Issue 5, Ver. I, PP 40-46, Oct 2015.

KOMMU PAVAN KUMAR

completed B.Tech from Nalanda Institute Of Engineering And Technology, kantepudi and pursuing M.Tech from Eluru College of Engineering & Technology, Duggirala Village, Eluru, Andhra Pradesh, India. His area of interest is VLSID.

#### SRIVENKATA SESHU ARAVIND

**R** completed M.Sc from AU Campus, VSP and M.Tech from Aurora's Astra, Hyderabad. At present he is working as associate professor in Eluru College of Engineering & Technology, Duggirala Village, Eluru, Andhra Pradesh, India. His area of interest is communication, VLSI.